Tool/software:

Hi

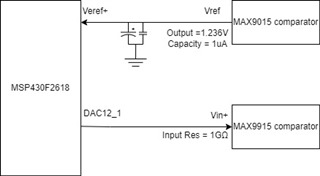

I'm using MSP430F2618 DAC12 modulel to generate an analog value as the Vin+ input of a comparator. the schematic is shown as following. The reference voltage is supplied by a MAX9015 which has 1uA output capacity.

First I set DAC12IR bit as 0, then the functionality of the circuit works good.

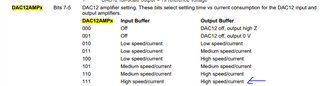

Then I want to increase the output resolution of DAC12 so I set DAC12IR bit as 1.

After that, I found the DAC12_1 port doesn't output properly and the Veref+ was pulled down. The datasheet and userguide dosen't say any thing about if the power consumption of DAC12 module will be increased due to DAC12IR. But the fact is that it seems so.

So my question why this issue occurs when DAC12IR bit is set?And is there any way to solve this issue without change hardware design?

Thank you!