Other Parts Discussed in Thread: TPS544C20, LM5066I

Tool/software:

Hi,

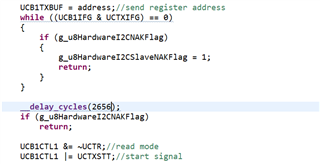

When I use I2C module of MSP430F5529, some problems happened. I use the following code to send one read-byte signal. (current MCLK is 32MHz)

The interrupt code is as following

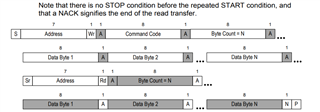

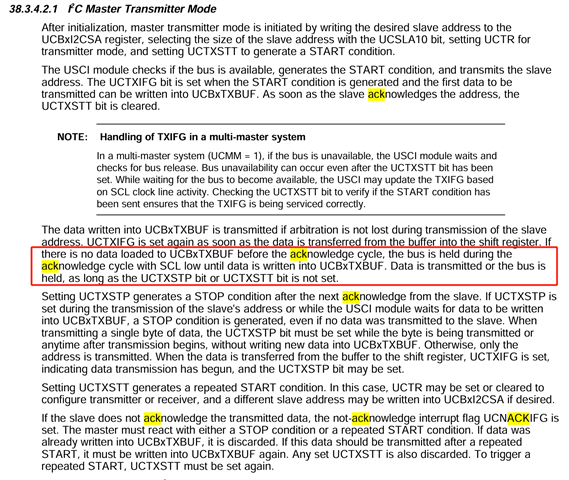

After I2C module initiation, I enable NACK interrupt, and start to transmit read-byte signal. The signal I want to send is as following

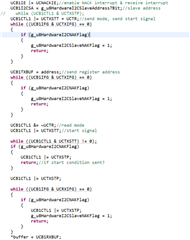

When I test if receive NAK reply before repeat start signal, something I does not expect happened, for example

I want to send stop signal when I receive NAK signal, in the above example, I want to send stop signal after receive 0x00[NAK], and the following read signal will not send any more, just like following

Is there any problem with my code? How can I change my code to realize the expected function and fix this problem?

Best Regard,

ZJY