Tool/software:

Hi,

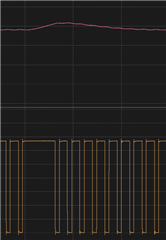

I'm working with the MSP430FR4276 microcontroller and encountering an issue while generating a PWM signal using Timer_A3. The PWM duty cycle needs to be adjustable at any time by my PI controller. However, I'm facing a problem (as shown in the attached image) that I believe is related to the timing of when I update CCR1.

It seems that if I update CCR1 at the wrong moment, the compare event between CCR1 and CCR0 doesn't occur until the timer reaches its maximum value. As a result, the new duty cycle only takes effect in the next cycle.

The challenge is that I don't want to stop the timer using the MC bits, nor do I want to use interrupts (ISRs). According to the datasheet, shadow registers are used for this purpose and should be automatically handled by Timer_A_initCompareMode(). Therefore, I expected that simply calling:

Timer_A_setCompareValue(TA3_BASE, TIMER_A_CAPTURECOMPARE_REGISTER_1, newDutyCycle);

void MY_TIMER_init(void)

{

// Set up Timer_A3 in Up Mode

Timer_A_initUpModeParam upModeParams = {0};

upModeParams.clockSource = TIMER_A_CLOCKSOURCE_SMCLK;

upModeParams.clockSourceDivider = TIMER_A_CLOCKSOURCE_DIVIDER_1;

upModeParams.timerPeriod = 0xFFF;

upModeParams.timerInterruptEnable_TAIE = TIMER_A_TAIE_INTERRUPT_DISABLE;

upModeParams.captureCompareInterruptEnable_CCR0_CCIE = TIMER_A_CCIE_CCR0_INTERRUPT_DISABLE;

upModeParams.timerClear = TIMER_A_DO_CLEAR;

upModeParams.startTimer = false;

Timer_A_initUpMode(TA3_BASE, &upModeParams);

// Configure CCR1 for PWM output

Timer_A_initCompareModeParam compareParams = {0};

compareParams.compareRegister = TIMER_A_CAPTURECOMPARE_REGISTER_1;

compareParams.compareInterruptEnable = TIMER_A_CAPTURECOMPARE_INTERRUPT_DISABLE;

compareParams.compareOutputMode = TIMER_A_OUTPUTMODE_RESET_SET;

compareParams.compareValue = 0x7FF;

Timer_A_initCompareMode(TA3_BASE, &compareParams);

Timer_A_startCounter(TA3_BASE, TIMER_A_UP_MODE);

}