Tool/software:

In my application, the main code starts and then enters LPM3 mode. The application exits LPM3 under the following conditions:

-

An interrupt occurs every 15.625 ms, and its ISR is served without exiting LPM3 mode.

-

Every 125 ms, the system exits LPM3 using the instruction

LPM4_EXIT, serves the super loop (while(1U)) once, and then returns to LPM3 mode. This cycle repeats every 125 ms. -

During both LPM3 and active modes, the UART remains active and operates using SMCLK, which runs at the same frequency as MCLK (8 MHz).

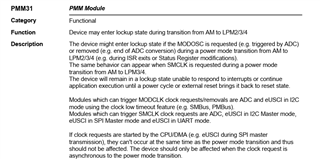

Given the conditions described above, does this scenario fall under the device erratum stating:

"Device may enter lockup state during transition from AM to LPM2/3/4. When SMCLK is requested during a power mode transition from AM to LPM3/4."

If it does then how to exit this lockup state.