Other Parts Discussed in Thread: MSP430FR6007, MSPM0L2228, MSP430FR6047

Tool/software:

Hi,

I am trying to send data between two LP-MSPM0L2228 boards using UART1 on both boards.

Our final use case is a setup where we need to operate in low power mode most of the time, which means that we cannot use HFCLK - hence LFCLK (LFXT 32.768 kHz) is chosen.

The UARTs must communicate at 9600 baud with 8 data bits, no parity and 2 stop bits to work with our existing setup, which consists of MSP430FR6007 devices along side non-TI devices all running their UARTs from a 32.768 kHz crystal.

When testing I use the "uart_echo_interrupts_standby" example and then I switch to LFXT and UART1 on pin PA8 + PA9. Furthermore, I have enabled CLKOUT on pin PA27 for the LFCLK.

For the RX project I have in addition a debug pin on PA25 indicating whenever the sample code detects an inconsistency in the received data.

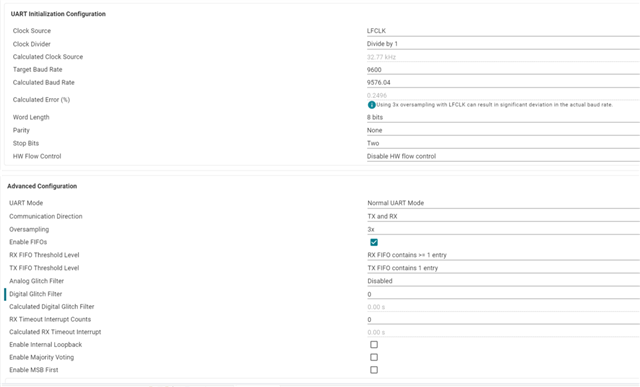

If I set the following settings for the UARTs I get error free communication:

Source: MSPM0L2228 8N2 at 9576.04 baud -> Destination: MSPM0L2228 8N1 at 9709.04 baud -> OK

Source: MSPM0L2228 8 <Stick One> 1 at 9576.04 baud -> Destination: MSPM0L2228 8N1 at 9709.04 baud -> OK

If I set the following symmetric settings for both UARTs I do not get error free communication:

Source: MSPM0L2228 8N2 at 9576.04 baud -> Destination: MSPM0L2228 8N2 at 9576.04 baud -> FAIL

Source: MSPM0L2228 8E1 at 9576.04 baud -> Destination: MSPM0L2228 8E1 at 9576.04 baud -> FAIL

1) When I set up 2x MSPM0L2228 evaluation modules. One for TX and one for RX with the same settings (baud rate, parity and stop bits) then I do not get error free communication - how come? Am I setting up my project wrong or is this behavior to be expected?

I also struggle getting our non-TI processor to receive an error free transmission from the MSPM0L2228. Though we previously have had the non-TI processors receiving flawlessly from MSP430FR6007.

2) Are there more parameters that I can adjust/tweak on the MSPM0L2228 in order to make the non-TI processor correctly receive a transmission from the MSPM0L2228. So far I have adjusted parity and stop bits along with baud rate (IBRD + FBRD)?

3) As far as I recall the MSP430FR6007 had a register where we could modify the bit modulation pattern. How exactly does the integer and fractional part of the MSPM0L2228 work and could that explain why we see our communication failing?

In the following I have provided 3 pictures showing what the logic analyzer has captured while two MSPM0L228 modules are communicating with each other.

Both boards are set up with 8 data bits, no parity and 2 stop bits – and a baud rate of 9576 (via syscfg).

The transmitting code sends a byte - increment it and sends it again.

The receiving code receives a byte and validates that it is one higher than the previous received byte - if not it toggles PA25 - regardless of if it was a match or not the byte is transmitted.

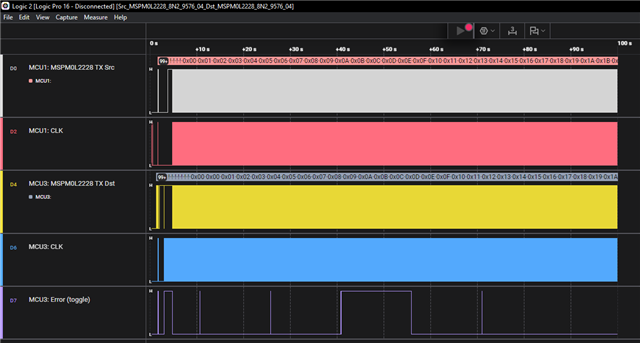

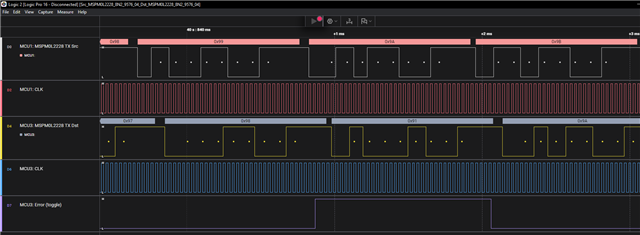

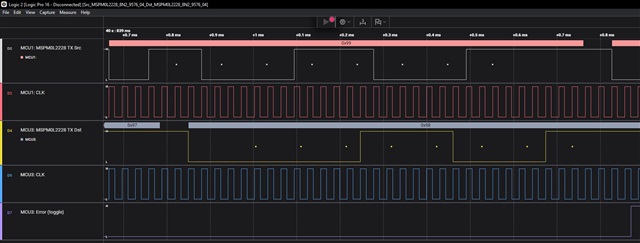

MCU1: MSPM0L2228 TX Src // TX from the source MSPM0L2228 board // (PA8_UART1-TX (Source MSPM02228 board))

MCU1: CLK // LFCLK from the source board // (PA27 (Source MSPM02228 board))

MCU3: MSPM0L2228 TX Dst // TX from the destination MSPM0L2228 board (the board echos out what it received from the source board) // (PA9_UART1-RX (Destination MSPM02228 board))

MCU3: CLK // LFCLK from the destination board // (PA27 (Destination MSPM02228 board))

MCU3: Error (toggle) // GPIO from the destination board that is toggled every time the board receives a byte out of sequence. Usually there will be two toggles right after each other – one on each side of the incorrect byte // (PA25 (Destination MSPM02228 board))

PA8_UART1-TX (Source MSPM02228 board) connected to PA9_UART1-RX (Destination MSPM02228 board)

Ground connected between the two boards.

First picture shows the entire communication (100s) between the two boards. Every state shift in the MCU: Error (toggle) indicates a byte received out of sequence.

Second picture shows a close up on one of the errors. The byte 0x99 is incorrectly received as 0x91.

The last picture is further zoomed in so the clocks from both boards are easier to see.

Let me know if more info is needed.

Regards

Bue