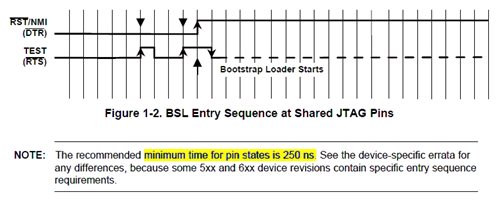

I need clarification on the SYS10 bug that exists in non-Rev. F versions of the MSP430F543xA devices. Per the MSP430F541xA_3xA device Erratasheet slaz057n October 2009-Revised December 2011, it mentions that the low phase of teh TEST pin must not exceed 15us during the BSL entry sequence. However, the MSP430 Programming Via the Bootstrap Loader (BSL) Users Guide - slau319b (revised March 2012) in Section 5.1 (page 33), the BSL version for the MSP430F543xA, the 2ns statement for known bugs, says that to invoke the BSL using TEST/RESET, the 2nd low pulse on TEST must be shorter than 15us. My questions is, does that mean all other pulses are don't care, or should they also be < 15us?

I've attached a scope plot below showing the sequence that we're trying to implement in order invoke the BSL on the MSP430F5438A Rev. D device. The TEST pin "receives" three low pulses that are ~10us in duration while RESET is low. Therefore, it gets at least three positive edges while RESET is LOW. The TEST then stays HIGH once RESET transitions from LOW-to-HIGH. Any thoughts on if this would work? I've tried it using our Host program that command the BSL sequence and it does not appear to work yet. I'm trying to get opinions on if this sequence should work.