Hi,

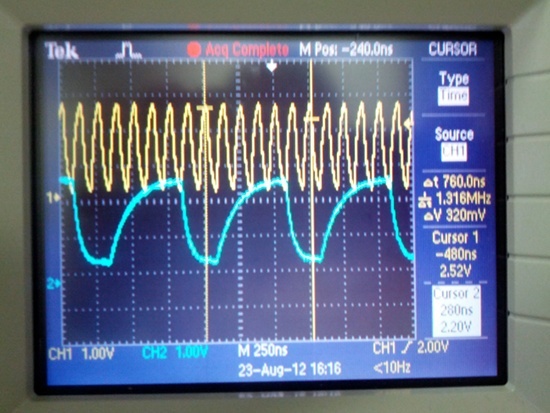

We are using MSP430F2012 USI I2C to driver an I2C slave EEPROM. The I2C clock is configured to use SMCLK with a divisor of 2 (divide by 4). SMCLK is configured to be the same as the MCLK from DCO at 8MHz. We expected that the I2C master clock to be 2MHz, but what it really came out of the USI, measured only 1.3MHz, while the SMCLK being 8MHz correctly, see attached the scope shot (the yellow line is SMCLK and the blue line is the I2C clock). If we configure the divisor to 4, instead of getting an I2C clock of 1MHz, we only got about 750Khz, very strange. Can anyone please explain what's happening here? Thanks a lot.

Cheers,

Rong