I have a slave I2C setup using interrupts, and I see an extra interrupt that I can't account for. I'm doing a simple master-RX / slave-TX of 4 data bytes, and the master and slave both seem to operate correctly, and a bus-decode shows the expected activity. But the slave shows 5 TX interrupts, instead of the anticipated 4 - one for each data byte. The data is correct, nothing is missing, the master receives the correct data, so it must be working correctly as far as the data transfer goes. This is the first implementation of I2C on the MSP430 that I've done, so I want to be sure I'm not letting some bug get into my component code.

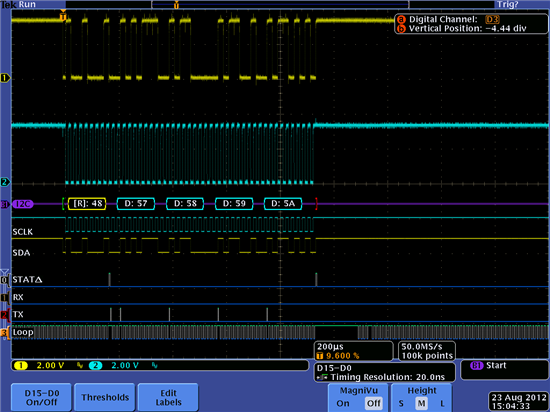

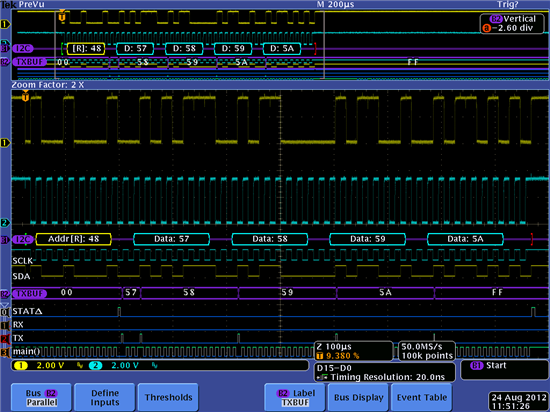

The following screen-captures illustrate the issue:

There are two TX interrupts close together, just after the START shown on STAT-change

Here is a closeup detail

The I2C Slave Transmitter Mode discussion says:

Then the address is acknowledged, the UCSTTIFG flag is cleared, and the data is transmitted. As soon as the data is transferred into the shift register the UCBxTXIFG is set again.

So it seems like this is normal operation, but I don't understand it fully. Could someone enlighten me on this, please?

- Ray