Other Parts Discussed in Thread: MSP430FR5739

Hi,

When working with timers in the MSP430FR5739 I can detect a certain delay (not constant and always in the range of µs) when switching on the signal and outputing the capture/compare unit output. I will expect having a delay of some nanoseconds but µs are a good bunch of cycles in between.

Does anyone know where does this delay come from? Is it possible to avoid it?

As an example for reproducibility I am using the next code:

#include <msp430fr5739.h>

;------------------------------------------------------------------------------

ORG 00FC00h ; Program Start

;------------------------------------------------------------------------------

RESET mov.w #01FFFh,SP ; Initialize stackpointer

StopWDT mov.w #WDTPW+WDTHOLD,&WDTCTL ; Stop WDT

mov.w #CSKEY, &CSCTL0

mov.w #DCOFSEL0+DCOFSEL1+DCORSEL, &CSCTL1 //DCO runing at 24MHz

mov.w #SELM__DCOCLK+SELA__DCOCLK+SELS__DCOCLK, &CSCTL2 //clocks running at 24MHz

mov.w #00h,&CSCTL3

bis.w #DIVA__2,&CSCTL3 //divide the auxiliary clock frequency by 2

bis.b #BIT0+BIT1, &P1DIR //output the timer signal in P1.1

bis.b #BIT0 + BIT1, &P1OUT

bis.b #BIT1,&P1SEL0 //secondary function selected in port direction

//timer setup for generating a 600KHz clock signal

bis.w #TAIDEX_4,&TA0EX0 //divide the frequency by 5, the auxiliary clock was already divided by 2 so we get f/10=1200KHz

mov.w #1,&TA0CCR0

mov.w #OUTMOD_4, &TA0CCTL2 //PWM output mode: 4 - toggle */

mov.w #1,&TA0CCR2

bis.w #TASSEL__ACLK+MC_3+TACLR,&TA0CTL // Timer A0 mode control: 3 - Up/Down */and Timer A source ACLK

FF: jmp FF

nop

;-------------------------------------------------------------------------------

COMMON INTVEC ; Interrupt Vectors

;-------------------------------------------------------------------------------

ORG RESET_VECTOR ; POR, ext. Reset

DW RESET

END

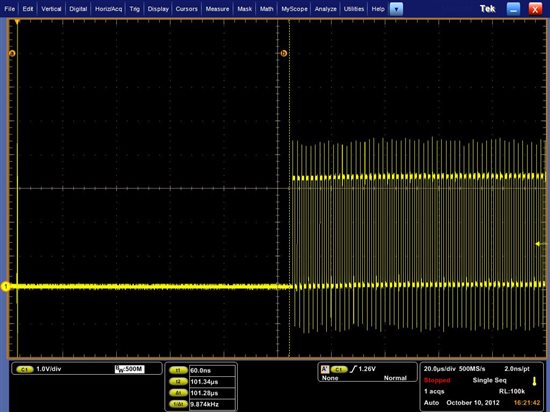

I attach the result that I get in the Osci when meassuring the output on the pin P1.1:

As shown in the Osci the delay between the port is switched to timer output mode (bis.b #BIT1,&P1SEL0 ) till we get the timer output is around 100µs. If we are working at

24MHz, these are 2400 cycles in between.

I would appreciate any help.

Thanks in advance.