As I wanted to use MSP430FR5738 for bluetooth sensor, I put 9600*3*32*16=14745600=14.7456MHz X'tal.

And try to set baud rate at 9600*3*32=921600=921.6kbps as follows,

UCA0CTL1 |= UCSWRST;

UCA0CTL1 = UCSSEL_2; // Set SMCLK as UCLk

UCA0BR0 = 1 ; // 1 = 921600 baud = 14745600/1/16

UCA0BR1 = 0;

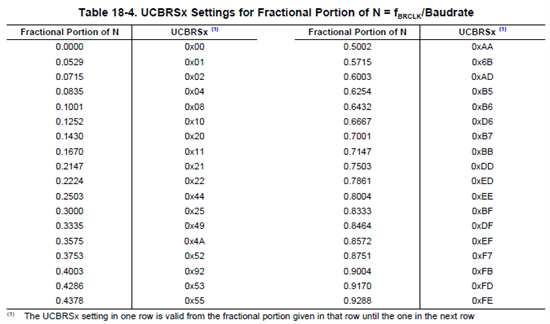

// UCBRSx = 0x00 upper 8bit, UCBRFx = 0x0 4bit, UCOS16 = 0x1 4bit

UCA0MCTLW = 0x0001 ;

P2SEL1 |= BIT0 + BIT1; // pin selection for TXD and RXD

P2SEL0 &= ~BIT0;

P2SEL0 &= ~BIT1;

But, I got the baud rate of 311.5kbps. (1bit = 3.21uS )

Where do I go wrong?

Would you please show me the sample code to set the baud rate at 921.6kbps in C code please?