As I understand it, the USxSTE pin functions as a "chip select" for the slave device in a SPI connection (although not in the traditional sense). Based on the SLAU144I, the slave output should be muted if USxSTE is set to slave-inactive.

16.3.4.1 Four-Pin SPI Slave Mode

In 4-pin slave mode, UCxSTE is used by the slave to enable the transmit and receive operations and is

provided by the SPI master. When UCxSTE is in the slave-active state, the slave operates normally.

When UCxSTE is in the slave- inactive state:

• Any receive operation in progress on UCxSIMO is halted

• UCxSOMI is set to the input direction

• The shift operation is halted until the UCxSTE line transitions into the slave transmit active state.

However, this does not appear to be happening in my Launchpad testing.

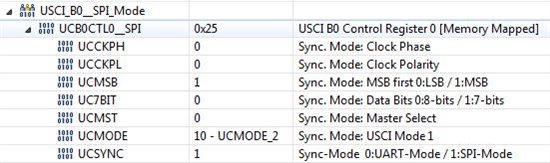

I have set UCMODE to UCMODE_2 and mode to SPI slave.

The SPI output works properly when I use STE=low as an chip select (CSN in the snapshot below):

However, since I have other SPI devices on this bus, I want the MSP430 to be disabled when I set CSN (chip select negative) high (inactive). But this does not seem to work properly. In the snapshot below I hold CSN high, but the spi slave (MSP430) continues to send data to the bus.

AM I MISUNDERSTANDING THE FUNCTIONALITY OF THE USxSTE PINS? Is there some configuration parameter I am missing? Any suggestions would be appreciated.