This present question is targeted to the engineering team at TI. In recent years I have discussed the matter with several experts in industry and book authors. TI seems to be the only company that shows 2^n-1 factor on ADC conversion equation (where "n" is the ADC resolution). In the past, the subject has been discussed a few times, but I think that TI could answer it once and for all.

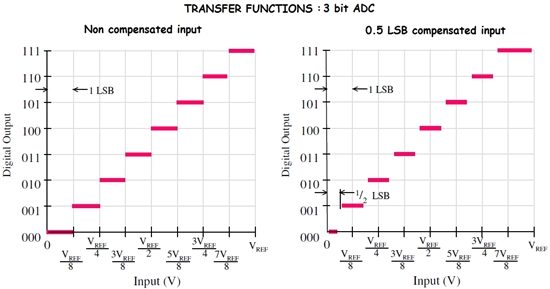

For example, consider an ideal 3 bit ADC transfer function (figure below): The vertical axis shows seven intervals (2^n-1) and horizontal axis shows eight intervals (2^n). This is true also for 0.5 LSB input compensated ADC. The final transition (from 110 to 111) occurs when input reaches 1 LSB below Vref or 1.5 LSB below Vref. In other words, the transfer functions are something like:

1. For an ideal 3 bit ADC with no compensation on input:

Nadc = int (Vin/Vref*8)

2. For an ideal 3 bit ADC with 0.5 LSB compensation on input:

Nadc = int ((Vin + 0.5 LSB)/Vref*8)

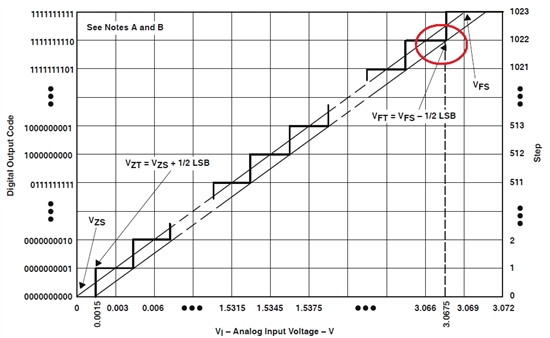

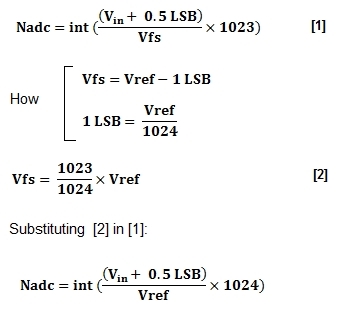

So, with n = 10, the discussion moves to 1023 and 1024 factors. The point is that virtually all the other microcontrollers (Renesas, Atmel, NXP, Freescale, ...) exhibit the 2^n factor on equation conversion (than 2^n-1) on its embedded ADCs. I think it would be very interesting to see a conversion plot, similar that below, for TI microcontrollers (ex. MSP430); but no one can find it.