Dear MSP430 experts,

I tested the I2C example codes of repeated START from 430ware, they are "msp430g2xx3_uscib0_i2c_12(&13).c"

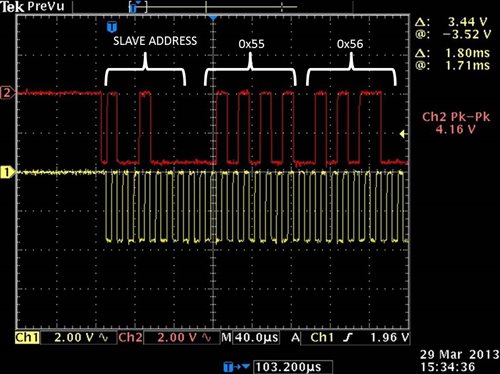

The waveforms of SDA and SCL shown on oscillator really bothers me. My devices are two G2553 EVMs.

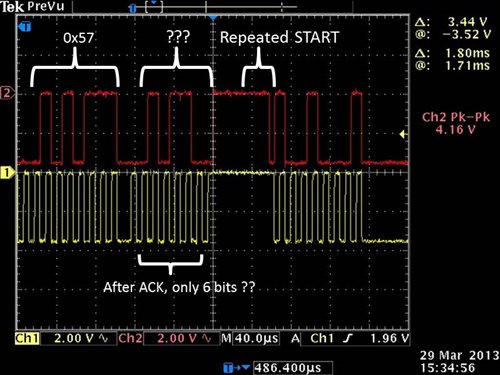

I printed the waveforms. The first time master transmits data to slave, 0x55, 0x56, 0x57, and after 0x57 comes with a only 6 bits something

It seems to be 0x58 but the code only transmits 3 bytes at a time. So what is that ?

After master TX (0x55, 0x56, 0x57), then slave TX (0x11, 0x12), and continue with master TX (0x5A, 0x5B, 0x5C), some bytes lost !?

0x58 & 0x59 didn't show on the oscillator. This also happen when slave TX again, 0x13 didn't appear but starts with 0x14 and 0x15.

Could someone explain this or has the same question? Thanks in advance!