Hi,

I've saw that some people already faced to interface the MSP430 and the ACC ADXL345.

I'm trying to establish a SPI 3 Wire communication between both devices, I'm able at least to produce the commands, but I do not receive any data from the device.

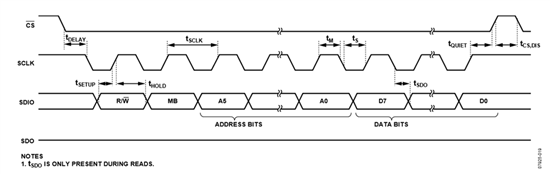

I actually verified with the oscilloscope and I realised that CS (Chip Select) is not behaving as desired:

source: Datasheet ADXL345 http://www.analog.com/static/imported-files/data_sheets/ADXL345.pdf , page 16

I saw in the ocsilloscope is not comming in phase, sometimes is delayed. Here it is my code:

void main (void) //Main routine

{

WDTCTL=WDTPW+WDTHOLD; // turn off Watchdog

P10SEL|= BIT1 + BIT2 + BIT3; // PSEL, SPI for SPI configuration

P10DIR|= BIT0; // CS pin

UCB3CTL1|=UCSWRST; // **Put state machine in reset** !!!

UCB3CTL0|=UCSYNC | UCMST | UCMSB | UCCKPL; // SPI 3 WIRE, Iddle High, Master Mode, MSB

UCB3CTL1|=UCSSEL_2; // Select SMCLK

UCB3BR0=0x02; //Set up SPI CL UCA3BR0 und UCA3BR1, (UCAxBR0 + UCAxBR1 ? 256)

UCB3BR1=0;

UCB3IE|=UCRXIE + UCTXIE; // Allow interrupts

UCB3CTL1&=~UCSWRST; // Init state machine

while (1)

{

SPI_3_ADXL345(); // Call function, write & read

}

}

void SPI_3_ADXL345()

{

//Writing some required configuration parameters on the ADXL

P10OUT&=~BIT0; // Set CS as LOW, beginning of transmission

__delay_cycles(2);

while(!(UCB3IFG&UCTXIFG));

UCB3TXBUF=0x31; // Resgister address, 0x31

while(!(UCB3IFG&UCTXIFG));

UCB3TXBUF=0x4E; //Configurate 0x31 with 0x4E

__delay_cycles(2);

P10OUT|=BIT0; // Set CS as HIGH, end of transmission

__delay_cycles(10);

//Retriving Device ID ADXL

P10OUT&=~BIT0; //Set CS as LOW, beginning of transmission

__delay_cycles(2);

while (!(UCB3IFG&UCTXIFG));

UCB3TXBUF=0x80; //Retrieve Device ID

while (!(UCB3IFG&UCRXIFG));

Test=UCB3RXBUF;

__delay_cycles(2); // Set CS as HIGH, end of transmission

P10OUT|=BIT0;

}

}

I realized that when I'm not transmitting, I don't have clock signal, how can the ADXL send its data to the MSP? ... weird :S

Any suggestion or correction is very well received.

Thanks and regards!

David