Hi all.

I'm using the MSP430FG4618 to control the TRF7970a NFC chip (by TI), hopefully making the two interact via SPI communication.

I'm quite new to MSP430, and I need to make a data_clk (aka SPI_CLK) triggering the SPI from the MCU to the NFC chip.

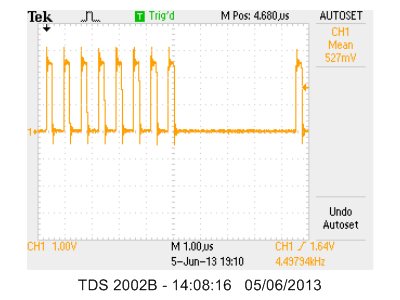

I have some sample code d/l from TI, showing how to create this clock, but it's not totally understandable to me, plus the clock signal is a bit jerky and has weird 'duty cycle' (see figure).

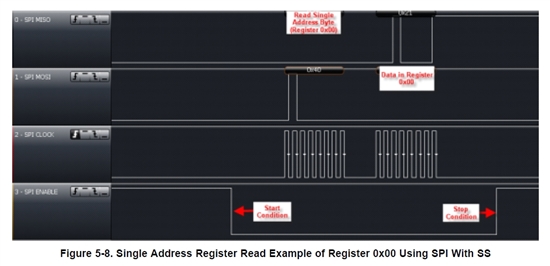

According to the NFC chip's manual, I need this duty cycle behavior for some reason, but I don't understand how is it controlled by the code.

SO - can anyone give me a code for a function that generates an SPI clock at about 2MHZ, and explain to me how to obtain this 'pull-down' behavior, like in this figure?

btw - output signal should be on P3.3

Thanks