Hi

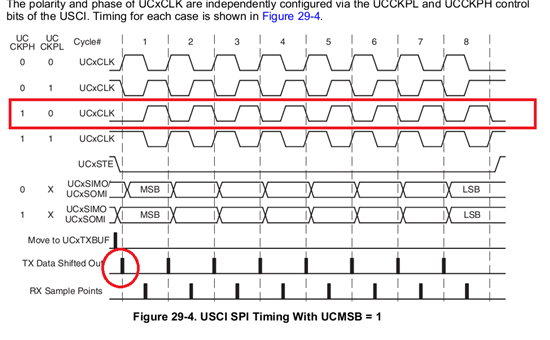

I'm using USCI_A on a msp430f5419A set into slave mode: 3 pin , clock idle low, sample on first edge ( ie rising edge ).

At startup everithing works fine. As it's a slave destinated to work in harsh environment I simulated some spurious clock coming in.

The peripheral looses synchronization accounting for the number of spurious clock received as I expected so I thought to reset the spi at the end of a wrong received frame.

I simply toggled UCSWRST. Now the strange behaviour: the reset doesn't work completly; it always leads the peripheral to a state in which it is out of sync of one clock ie it seems that after the reset it has already a bit in the receive shift register.

So if I inject five spurious clock then at first the peripheral is out of sync of 5 clocks, after reset it's out of sync of one clock.

If I inject three spurious clock then at first the peripheral is out of sync of 3 clocks, after reset it's out of sync of one clock.

Does anyone has any idea why this happens?

Any solution?