Other Parts Discussed in Thread: MSP430FR5739

Hi Everyone,

I'm experiencing problems trying to load code onto my MSP430 FR5739. I'm using the MSP-FET430 UIF with Code Composer 5.4 on Ubuntu 12.04.

I have an extremely simple test program (Code size=154 bytes) that loads every time without incident. As I try to load larger programs on to the controller, I start getting data verification errors. The frequency with which I get data verification errors seems to be dependent on the size of the code I am loading on to the controller. For example, I can successfully program the device ~1/3 times with a code size of 650 bytes and I cannot program the device at all with programs > 900 bytes.

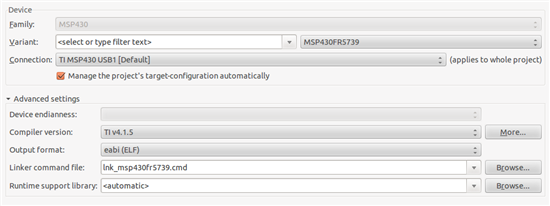

I have checked to make sure that the project device variant is in fact an MSP430FR5739, and that the project is using the appropriate linker file (see image).

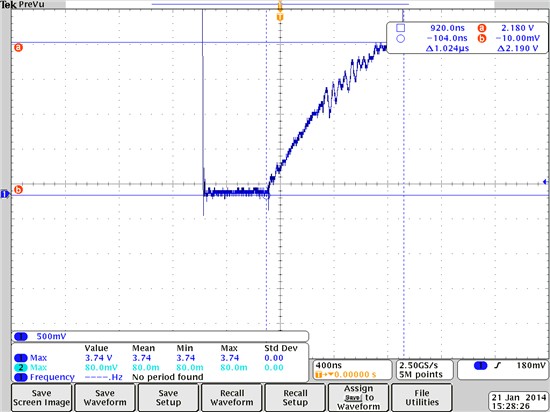

I've also checked the address at which the load error occurs and though the address changes every time, it is consistently located in the FRAM code memory as specified in the datasheet. Below are the addresses from the last 5 failed attempts at programming the controller:

0000C606, 0000C5FA, 0000C5E6, 0000C63A, 0000C5E4

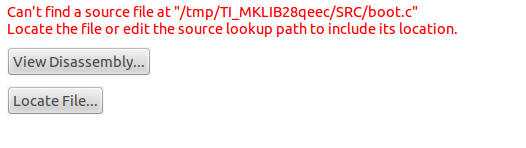

The data verification errors stop if I change the verification settings from Full to Fast, but then I get a new error:

I have checked TI's guide to troubleshooting data verification errors (http://processors.wiki.ti.com/index.php/Troubleshooting_CCS_-_Data_Verification_Errors) and I do not believe the examples described there pertain to my problem. That being said, I'd love to know if I overlooked something.

I would appreciate any solutions, insights or suggestions.

Thanks for the help!