In our application we are suffering from a lot of character loss (bad reception of characters) with IRDA transmissions from a certain device. I have tried to narrow down all the options that cause this but it still isn't fixed.Some background:

For receiving IRDA we use devices with a MSP430F2272 and a Vishay TFDU4101 IRDA transceiver. The bitrate is 57600 bps and with most other devices the setup works fine. The TFDU4101 however has a strange feature that might be the problem here but what I see happening in my test is not what I would understand from the data sheet of the MSP430:

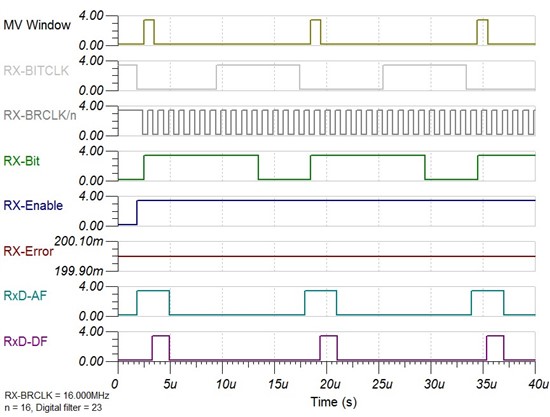

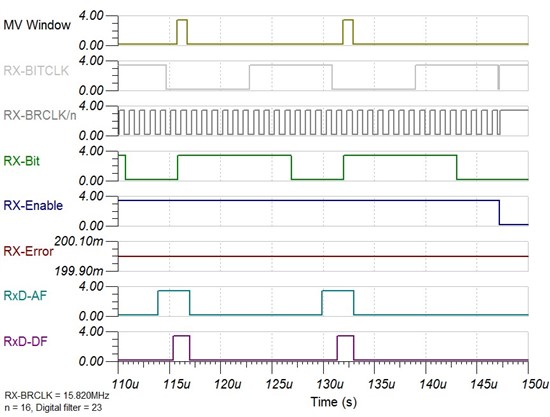

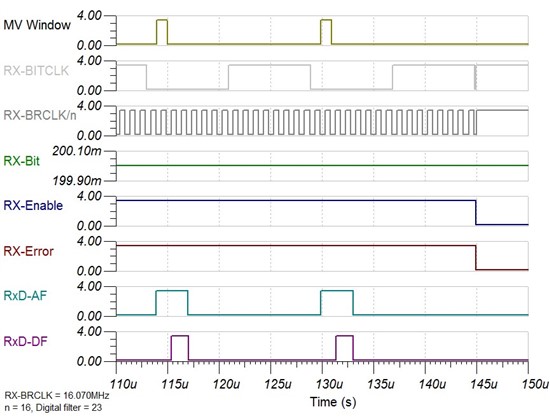

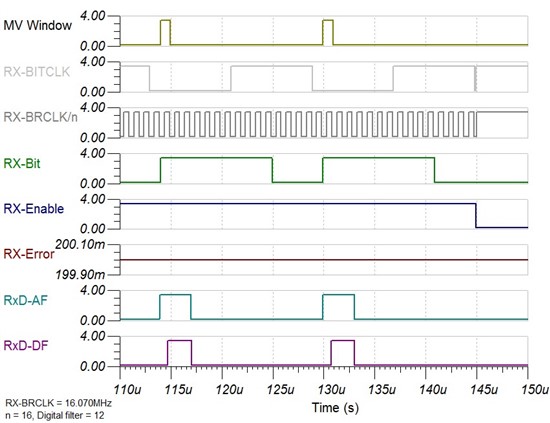

In 57600 communication a bit is 1/57600s long. This is 17.36uS. However in IRDA the bit is shaped to only 3/16 of this (hence the UCOS16=1 setting). That means that the bit is actually a light pulse of 3.255us. HOWEVER the TFDU4101 transceiver will transform each incoming bit (that is longer than 150ns) to a pulse of typically 2.2us.

I would therefore guess that the bad communication is caused by the source device having a clock that is slightly off, which is then 'amplified' by the fact that the incoming bit is changed in length from 3.255us to 2.2us. Taking the majority vote (as I undertsand from the literature is taken every 1/16 sample of the bitrate clock with UCOS16=1) would then fail often because the incoming bits are a bit off-sync but also shorter, thus causing the vote often to be '0' instead of '1',

If you take this logic a bit further then the following would happen: start communicating at 9600bps and all reception would fail, because a 9600bps IRDA light pulse is 19.53us long but our transceiver cuts this back to 2.2us! The 16x clock for this bitrate would be 153600 Hz. If a sample is taken using the majority vote, this would be done 3 (?) times every 6.51us, but our signal is no longer 19.53us long but only 2.2us. Thus the majority vote would always fail... This is not what happens! In our test setup (not using the device that causes bad reception on the MSP430 side, but a separate IRDA dongle) communicating at 9600bps over IRDA with this transceiver works just fine.

How can that be? Is the MSP430 maybe not taking a majority vote when IRDA is enabled (UCIREN=1). It seems so. If that is the case what causes the bad reception? Could a source clock being off just a little bit disturb the MSP430 because it samples the incoming bit once and at the 'incorrect time' (from this device's perspective) and this behaviour is worsened by the fact that the bit is also shorter than expected.

Some insights would be appreciated.