HI there,

We are trying to communicate data on UART. At first, we took example code from CCS for msp430f5529 (project name : "MSP430F55xx_uscia0_uart_04").This will echo data recieved at UART (baud 9600).

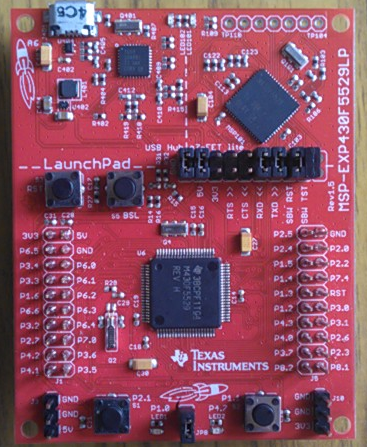

Launch Pad jumpers are connected as shown in the following picture.

1. We have opened Putty and configured it with same baudrate and 8bit data with one stop bit.

2. Connected Programmed LP to USB port of Laptop.

3. When we are trying to type charaters are Putty it is not echoing them. We tried with Hyper terminal also, but still the same problem.

4. Is there any connection on LP that we are missing ?

following is the code for it.:

#include <msp430.h>

int main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P3SEL = BIT3+BIT4; // P3.4,5 = USCI_A0 TXD/RXD

UCA0CTL1 |= UCSWRST; // **Put state machine in reset**

UCA0CTL1 |= UCSSEL_2; // SMCLK

UCA0BR0 = 6; // 1MHz 9600 (see User's Guide)

UCA0BR1 = 0; // 1MHz 9600

UCA0MCTL = UCBRS_0 + UCBRF_13 + UCOS16; // Modln UCBRSx=0, UCBRFx=0,

// over sampling

UCA0CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

UCA0IE |= UCRXIE; // Enable USCI_A0 RX interrupt

__bis_SR_register(LPM0_bits + GIE); // Enter LPM0, interrupts enabled

__no_operation(); // For debugger

}

// Echo back RXed character, confirm TX buffer is ready first

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=USCI_A0_VECTOR

__interrupt void USCI_A0_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_A0_VECTOR))) USCI_A0_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(UCA0IV,4))

{

case 0:break; // Vector 0 - no interrupt

case 2: // Vector 2 - RXIFG

while (!(UCA0IFG&UCTXIFG)); // USCI_A0 TX buffer ready?

UCA0TXBUF = UCA0RXBUF; // TX -> RXed character

break;

case 4:break; // Vector 4 - TXIFG

default: break;

}

}