Hi there,

I'm currently having an issue with using SPI to communicate with an external flash. I'm currently using DMA to send out SPI comms using the UCSI_B module.

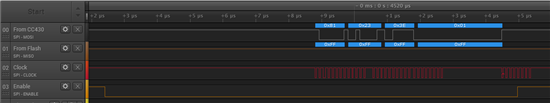

Most of the time this is working fine however sometimes I am occasionally getting errors when I communicate with the Flash chip and it doesn't hear me correctly. After a long time chasing this around I've discovered that it appears to occasionally miss a clock pulse. I've included an image below to help explain.

what should have occurred here is the the bytes [0x81][0x21][0x9F][0x00] should have been sent followed by an [0xFF] which would be sent during the point when the enable line is pulled back high. However as you can see this isn't what happened, looking closely you should be able to see that part way through the second byte the clock remains high for too long.

I'm currently running the USCI_B clock at 8Mhz, which is derived from a 24MHz source. I also ensured that when I recorded the data my sampling speed was high enough to avoid aliasing (sampled at 25MHz).

I've checked the errata (quick link here if you want to recheck) and I couldn't find anything that would obviously explain this so I'm hoping that someone on here might be able to offer some suggestions.

EDIT 1: The error occurs in different places, I send lots of different messages over the SPI lines, and I've seen the error occur in them all and in a different spot each time. I haven't noticed any pattern in the errors occurring.

Electrically the lines are short and scoping them reveals no obvious problems the rise times are well within what would be required and there is no visible rippling or noise from external sources.

There are several options for what the CPU may be doing during the DMA transfer, as there are several interrupts that could trigger duing this period, alternatively it may be sleeping. However this is unlikly to be the problem as the data does appear to have been inserted into the SPI buffer correctly, as adding a clock pulse to where it is missing would have provided the correct data. As such I believe the problem to be occurring after the DMA has completed its job.