Hi, ive been trying to trigger an adc12 repeat sequence of channels conversion from timer A1 (because these are the pin outputs i can verify on the launchpad board). The timer runs of an 32 kHz external crystal oscillator and i desire the ADC to sample at 8 kHz. I've looked at several forum posts but none have answered my questions and the data sheet/ user guide is vague on the relationships between the timer and ADC12 trigger.

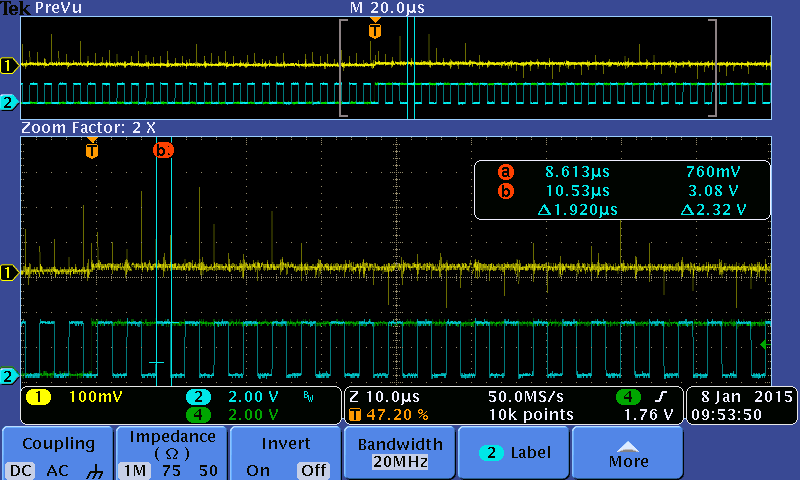

I set P3.6 to toggle to view timings on an oscilloscope. The PWM triggers correctly however the ADC triggers at around 600 kHz with the MCLK (still active. I have tried the setup from triggering a timer interrupt and starting the ADC via a software however I cannot get this to work.

Please find my code attached and any help would be very much appreciated.

#include <msp430.h>

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

// GPIO Setup // Configure GPIO for timer, set all registers to output to reduce current leaks

P1OUT &= ~BIT0; // Clear LED to start

P1DIR |= 0xFF; // Set P1.0/LED to output

P4DIR |= 0xFF;

P3DIR |= 0xFF;

P2DIR |= 0xFF;

PJDIR |= 0xFF;

P1OUT &= ~BIT0; // Clear LED to start

P1DIR |= BIT0; // Set P1.0/LED to output

P1SEL1 |= BIT1; // Configure P1.1 for ADC

P1SEL0 |= BIT1;

P3OUT |= BIT6;

P1SEL0 |= BIT2; // P1.2 options select

//configure gpio for adc

P1SEL1 |= BIT3 | BIT4 | BIT5; // Configure ADC inputs A1, A2 and A3

P1SEL0 |= BIT3 | BIT4 | BIT5;

//enable XTLFO gpio

PJSEL0 |= BIT4 | BIT5;

// Disable the GPIO power-on default high-impedance mode to activate

// previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

FRCTL0 = FRCTLPW | NWAITS0;

// Setup XT1 crystal.Set the Master and SM (16 MHz) and ACLK (XT1)

CSCTL0_H = CSKEY >> 8; // Unlock CS registers

CSCTL1 = DCORSEL | DCOFSEL_4; // Set DCO to 16MHz

CSCTL2 = SELA__LFXTCLK | SELS__DCOCLK | SELM__DCOCLK; // set ACLK = XT1; MCLK = SMCLK = DCO

CSCTL3 = DIVA__1 | DIVS__1 | DIVM__1; // Set all dividers

CSCTL4 &= ~LFXTOFF;

//Wait for the oscilator to settle

do

{

CSCTL5 &= ~LFXTOFFG; // Clear XT1 fault flag

SFRIFG1 &= ~OFIFG;

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

CSCTL0_H = 0; // Lock CS registers

ADC12CTL0 = ADC12MSC | ADC12ON; // Sampling time, ADC12 on

ADC12CTL1 = ADC12CONSEQ1 | ADC12CONSEQ0 | ADC12SHP | ADC12SHS_4; // repeat sequence of channels, triggers from TA1

ADC12CTL2 |= ADC12RES_2; // 12-bit conversion results

ADC12MCTL0 |= ADC12INCH_3; // Channel2 ADC input select; Vref=AVCC

ADC12MCTL1 |= ADC12INCH_4; // Channel2 ADC input select; Vref=AVCC

ADC12MCTL2 |= ADC12INCH_5 | ADC12EOS; // Channel2 ADC input select; Vref=AVCC

ADC12IER0 |= ADC12IE2;

ADC12CTL0 |= ADC12ENC;

//configure timer A1 for puslse width toggle option

TA1CCTL1 = OUTMOD_4; // CCR1 toggle and interrupt enabled

TA1CCR0 = 4-1;

TA1CCR1 = 0;

TA1CTL = TASSEL__ACLK | MC__UP | TACLR; // ACLK, up countmode, clear TAR

__bis_SR_register(LPM3_bits | GIE); // LPM0, ADC12_ISR will force exit

}

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = ADC12_VECTOR

__interrupt void ADC12_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(ADC12_VECTOR))) ADC12_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(ADC12IV, ADC12IV_ADC12RDYIFG))

{

case ADC12IV_ADC12IFG2:

P3OUT ^= BIT6;

break; // Vector 16: ADC12MEM2

default: break;

}

}