We've dug right down into TI-RTOS looking for the source of a very unusual problem.

We're seeing an interrupt flag set on a bit that hasn't experienced a transition. For PORT1, we have interrupts enabled for pins 2, 3, and 4. Currently it's hard-coded to transition on a LOW to HIGH for all 3 pins (see following screenshots) - all 3 set as input - and as far as the hardware registers are concerned, we're set to wait for a transition on any of those 3 bits.

However, that we're seeing is an interrupt on one of those three pins without a data transition on P1IN. I've set breakpoints in

"__interrupt Void ti_sysbios_family_msp430_Hwi47(Void)" to try to determine what's happening, but to no avail.. by the time we're in there, all I see is the same data as before the ISR triggered. Very puzzling.

Here is a screenshot of the PORT1 BEFORE the interrupt generated:

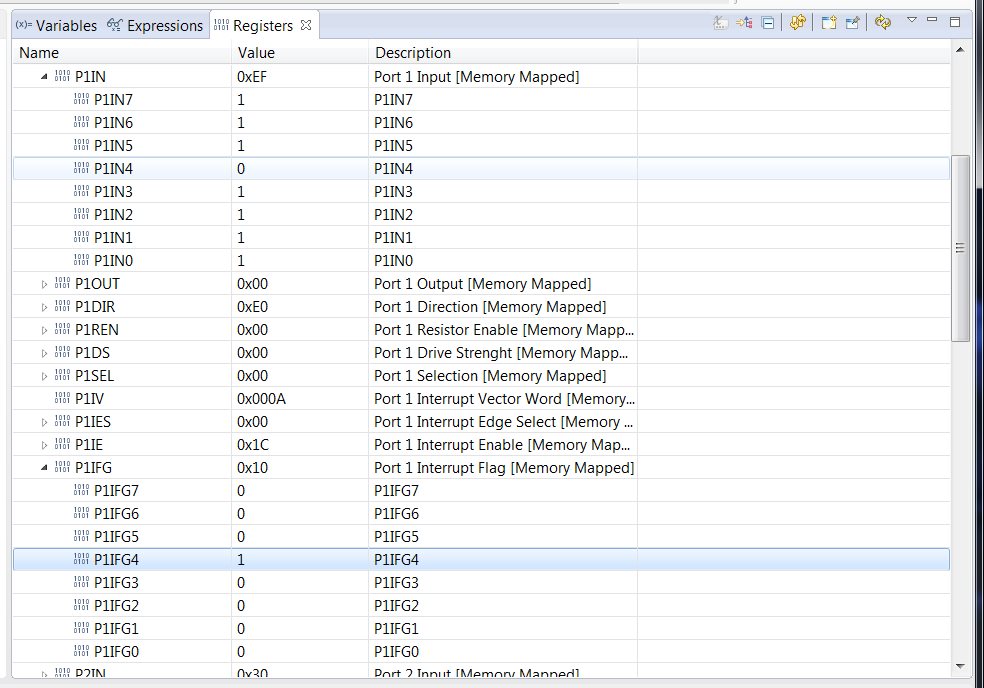

..and here is a screen-shot after the interrupt has triggered:

..and you can see that, while P1IN hasn't changed, I see P1IFG.4 set (and of course an interrupt triggered).

Can you provide some guidance as to how we might trace down where this might be coming from? We've put a scope on those input lines and the scope isn't seeing a data transition, either.

All help GREATLY appreciated!

Ed Averill