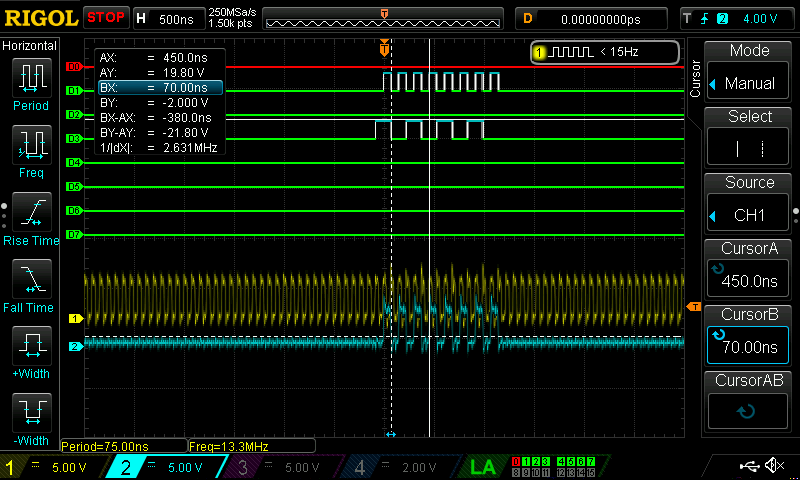

At the moment, the SPI clock rises at the second half of the cycle and falls at the end of the cycle. How could the SPI clock rise at the begin of the cycle and fall at the second of the cycle?

The SPI is set to master mode 1.

UCA0CTL0 |= UCCKPH + UCMSB + UCMST + UCMODE_0 + UCSYNC;