Hi,

I am using 'MSP430F5438A' micro controller , I am facing an issue in recent times though it is used from past 3 years.

Back Ground of Application: On Switch Press ,12v supply has to be enabled to the other boards connected to it.

Issue : In recent times observed a Reset of micro controller by External Watch Dog, where refresh of External watch dog performed in while(1).

In the debugging identified 2 Behaviors.

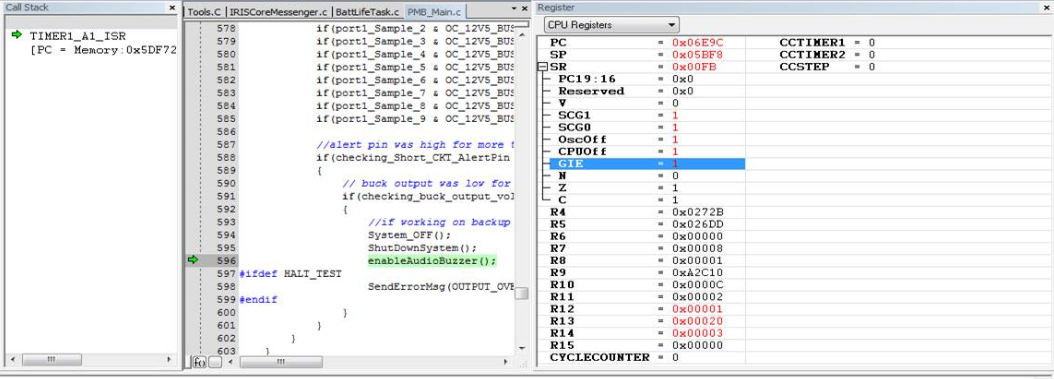

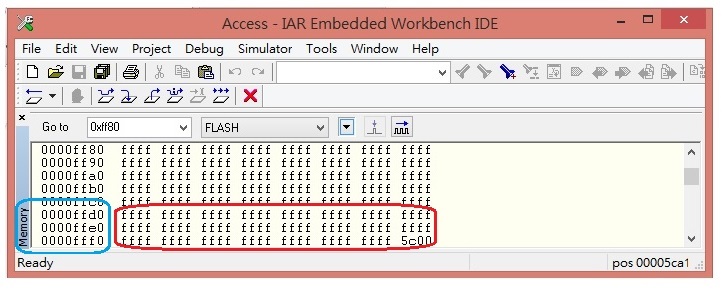

1.After Switch Press, Main while(1) is not getting executed, but interrupts are getting served. SYSNMI interrupt are getting triggered infinitely. Also observed that when SYSNMI is triggered 'VMAIFG' Flag is set.

2.Other behavior is after switch press,if i try to keep break points getting a warning:CPU is OFF and Further debugging is not possible then i checked CPU Register status CPU OFF,OSC OFF,SCG0,SCG1 bits are set.

Needed help in understanding the reason to cause this behavior.

Thanks in Advance.

Regards,

venkatesh