Other Parts Discussed in Thread: MSP430F6779A

I am using the DMA and SPI to transfer data between two MSP430F6779A's.

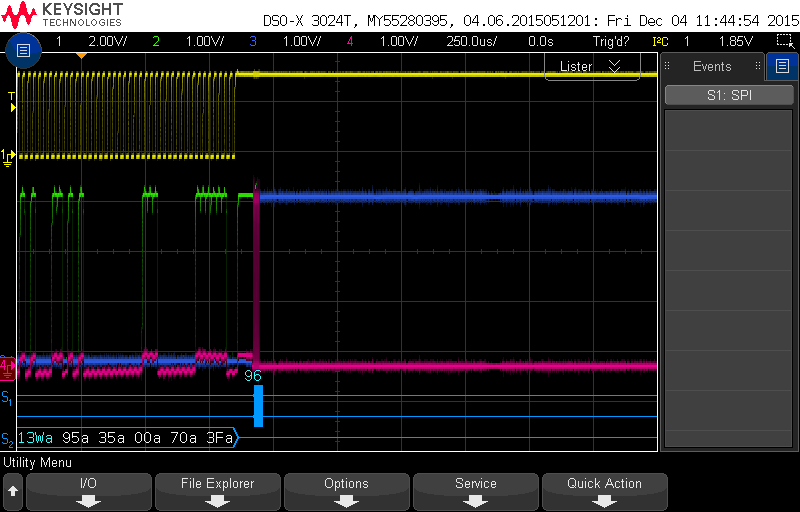

I am sending 114 bytes at a time and most of the time it works but sometimes it sends fewer bytes than it should.

After looking at the erratasheet I suspect that I am running into DMA9. One of the suggested workarounds to use a second DMA channel of lower priority. I don't quite understand how this would work for two reasons:

1) I am seeing partial packets being sent which means that the second DMA channel needs to know how many bytes to send based on how far the first one got. I don't think this is possible

2) for the SPI master I need to both transmit and recive which uses two DMA channels so with the workaround I would need 4 DMA channels but, the MSP430F6779A only has 3.

Can someone tell me if this is what DMA9 looks like and how to properly implement the workaround as described in the erratasheet?

The errata claims that this is fixed in RevC of this chip. All my chips are RevB. Is there a way to purchase RevC chips? This would be ideal as I could avoid this annoying bug.