Hello:

I have a question about SMCLK maximum frequency. I was setting the Clock System of my MSP432 when I came across with the following statement in the MSP432 User Guide (SLAU356A, page 292):

SMCLK uses the HSMCLK clock resource selection for its clock resource... SMCLK is limited in frequency to half of the rated maximum frequency of HSMCLK.

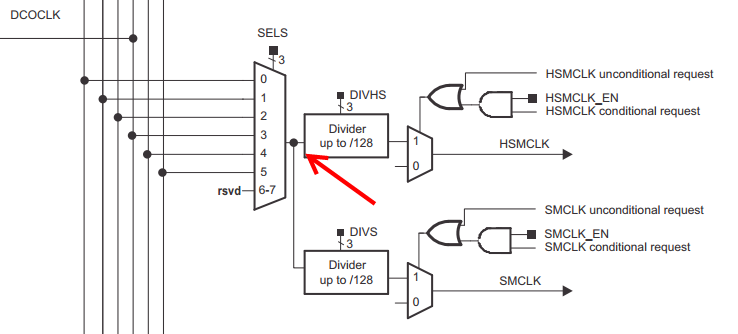

But, by checking the Clock System diagram in the same user guide (page 293):

I can't understand that limitation, once the clock source is the same, as indicated by the red arrow, both for HSMCLK and SMCLK. What provides the referred limitation? It would be helpful to obtain further explanations about it.

Thanks!