Other Parts Discussed in Thread: MSP-FET

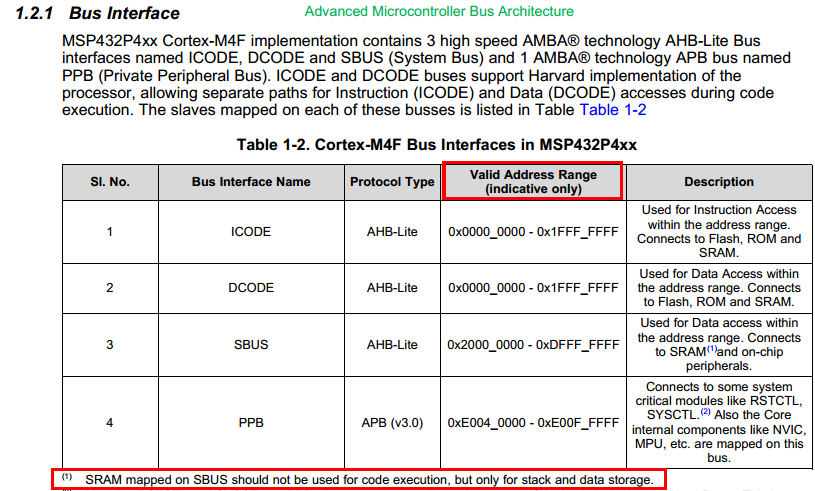

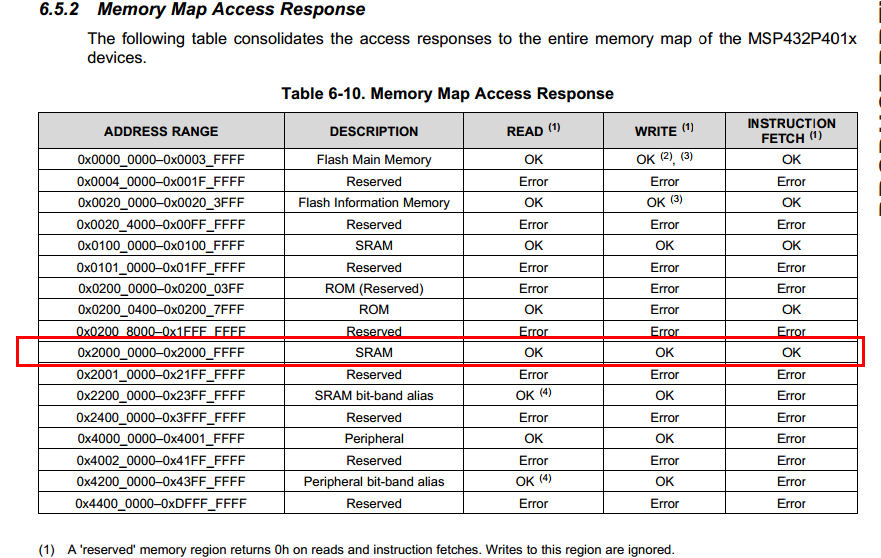

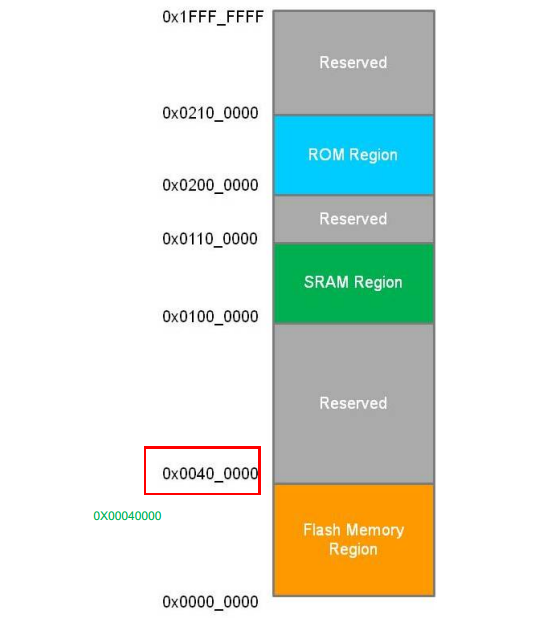

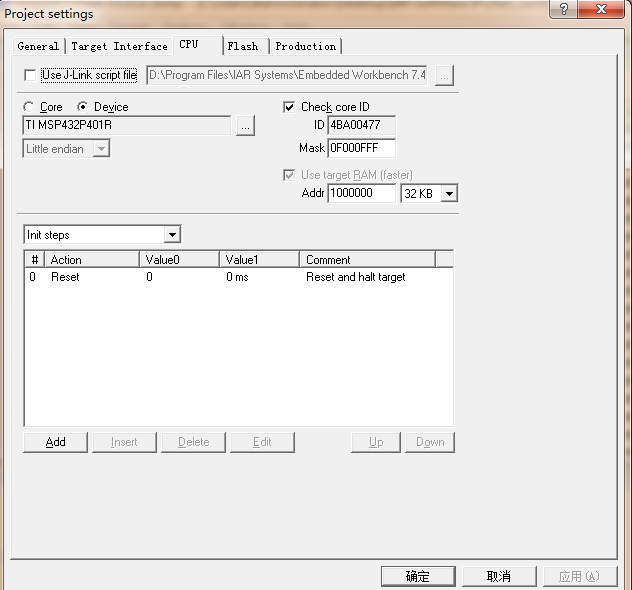

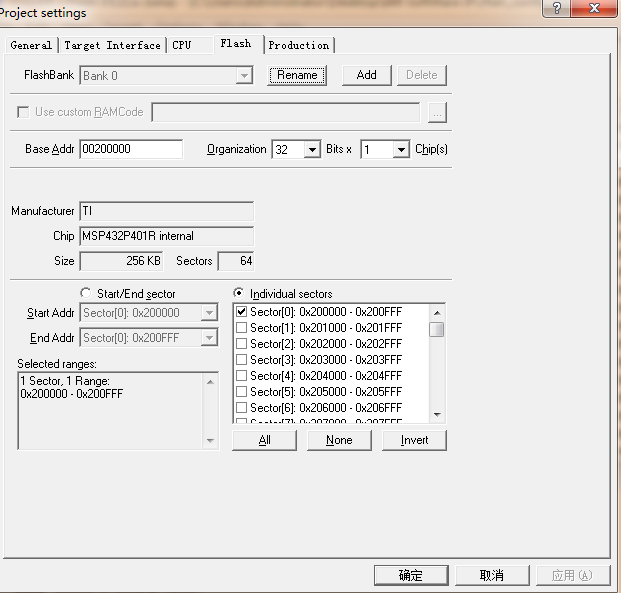

Hi, I want to locate my code to SRAM and excute in it , i have changed the icf file as below:

so i want to store my code to 0x20000000-0x20001FFF,and using 0x20002000-0x20003FFF for data(real RAM)

After doing that the runtine do not excuted as expecte,why this happened?

so i want to ask TI's employee, whether we can do it or not?

or is there any other methods to realize it ?

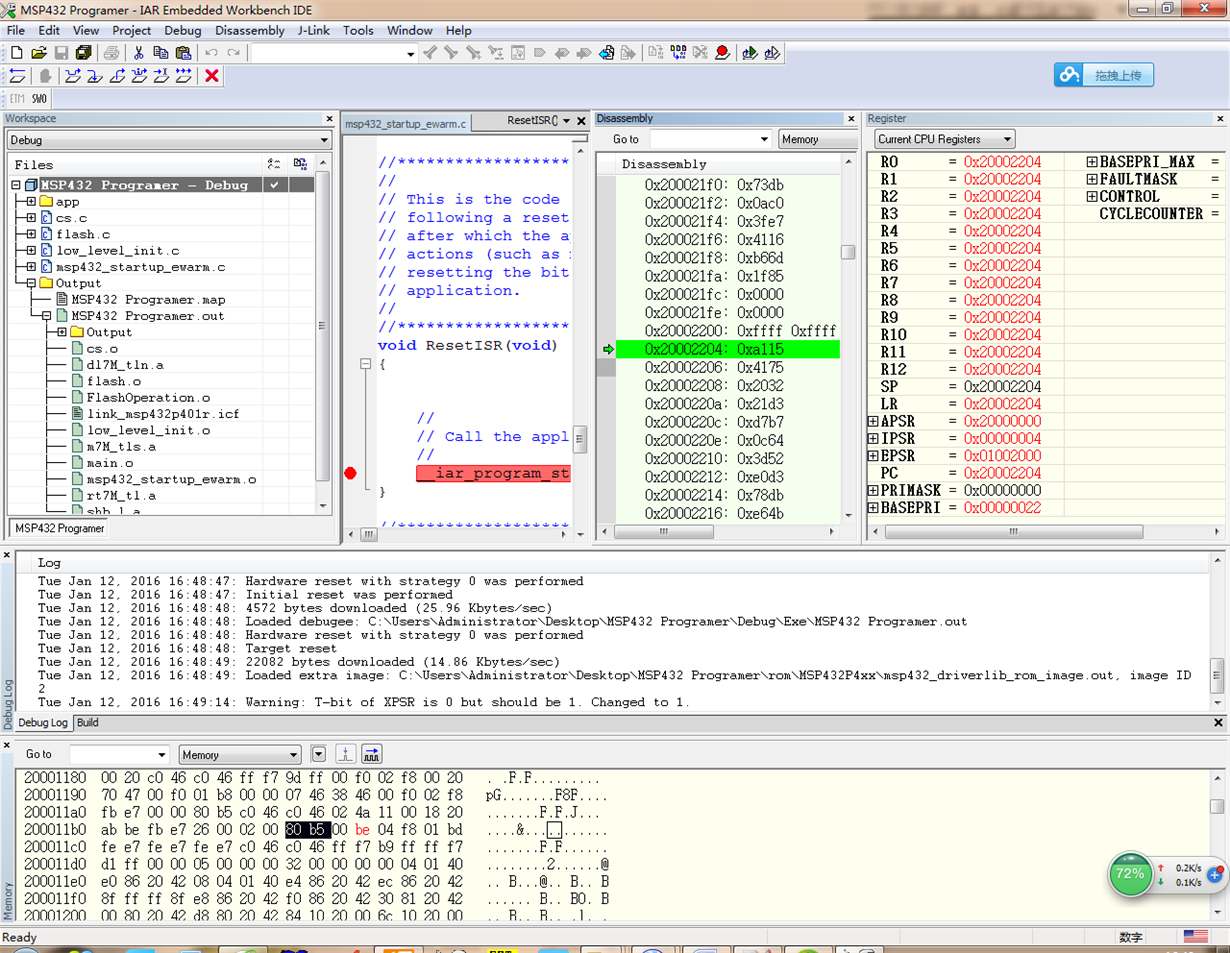

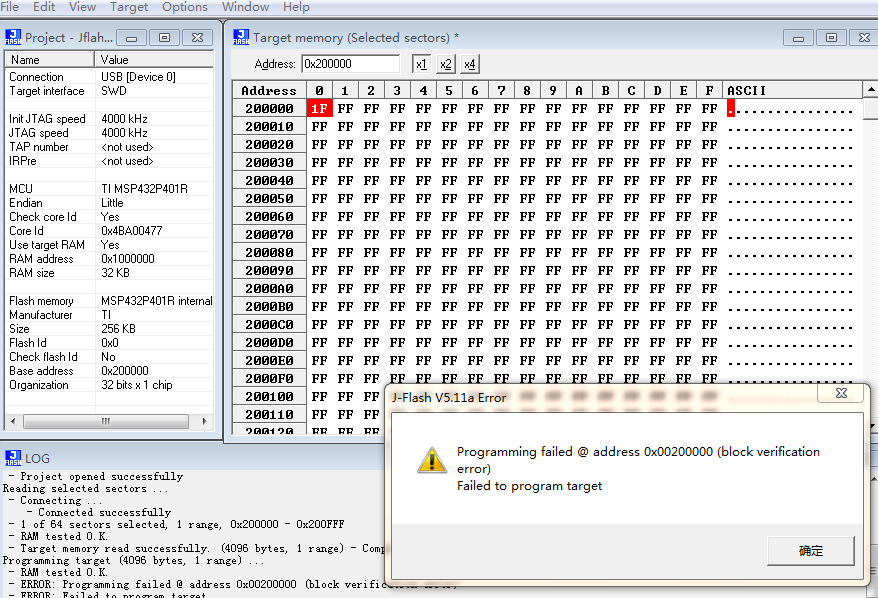

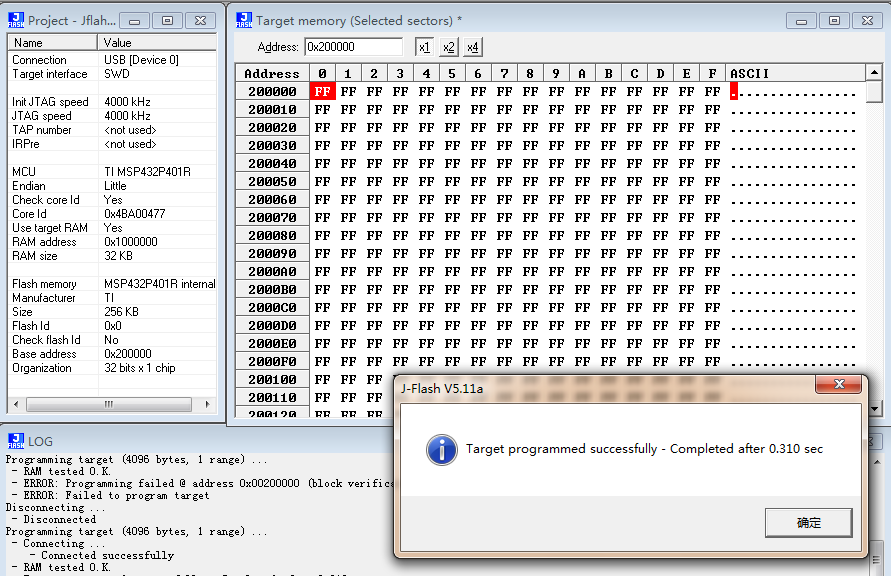

1、start debugger

2、sigle step error ocurrs

/*###ICF### Section handled by ICF editor, don't touch! ****/

/*-Editor annotation file-*/

/* IcfEditorFile="$TOOLKIT_DIR$\config\ide\IcfEditor\cortex_v1_0.xml" */

/*-Specials-*/

define symbol __ICFEDIT_intvec_start__ = 0x20000000;

/*-Memory Regions-*/

define symbol __ICFEDIT_region_ROM_start__ = 0x20000000;

define symbol __ICFEDIT_region_ROM_end__ = 0x20001FFF;

define symbol __ICFEDIT_region_RAM_start__ = 0x20002000;

define symbol __ICFEDIT_region_RAM_end__ = 0x20003FFF;

/*-Sizes-*/

define symbol __ICFEDIT_size_cstack__ = 0x1000;

define symbol __ICFEDIT_size_heap__ = 0x2000;

/**** End of ICF editor section. ###ICF###*/

define memory mem with size = 4G;

define region ROM_region = mem:[from __ICFEDIT_region_ROM_start__ to __ICFEDIT_region_ROM_end__];

define region RAM_region = mem:[from __ICFEDIT_region_RAM_start__ to __ICFEDIT_region_RAM_end__];

define block CSTACK with alignment = 8, size = __ICFEDIT_size_cstack__ { };

define block HEAP with alignment = 8, size = __ICFEDIT_size_heap__ { };

initialize by copy { readwrite };

do not initialize { section .noinit };

place at address mem:__ICFEDIT_intvec_start__ { readonly section .intvec };

place in ROM_region { readonly };

place in RAM_region { readwrite,

block CSTACK, block HEAP };