Dear All,

I am trying to write data into 2 Kbyte EEPROM interface with my MSP430F67779A using I2C.

Hardware connection is perfect and generating I2C clock of 400 KHz looking perfect.

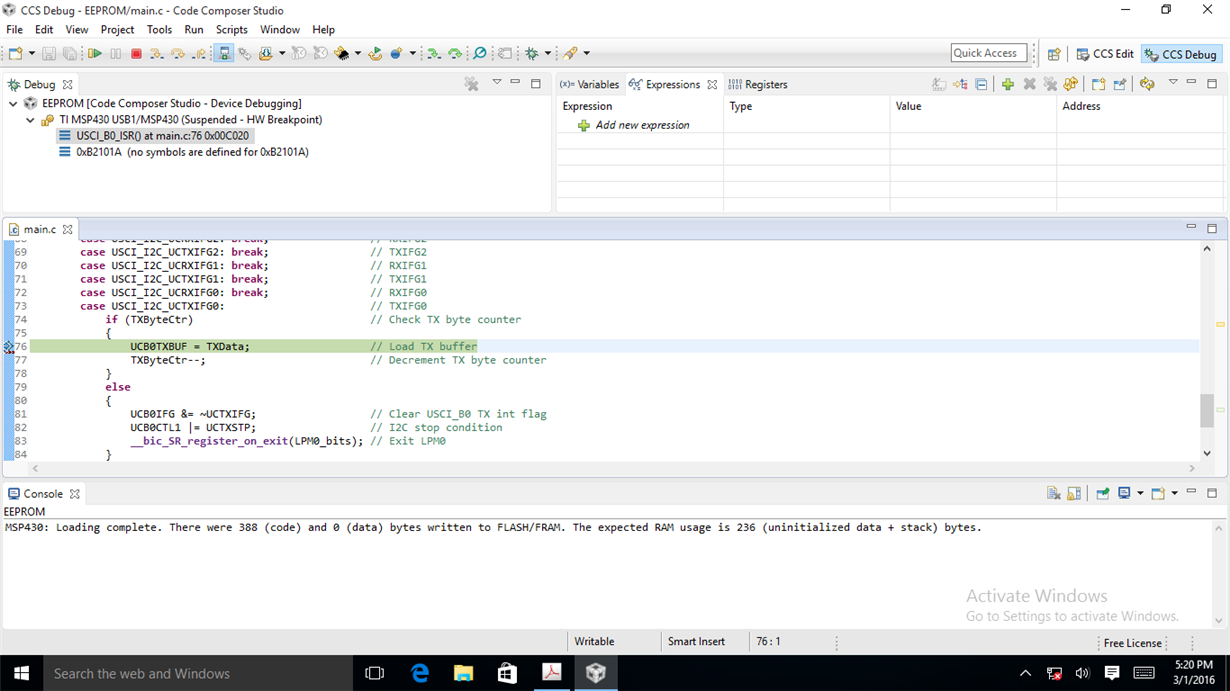

I am trying to write 0x12h data on 0x0000h location of EEPROM. so after I2C initialization and start I2C, in MSP430 It is going once in ISR and send only higher byte of address and then never come ISR.

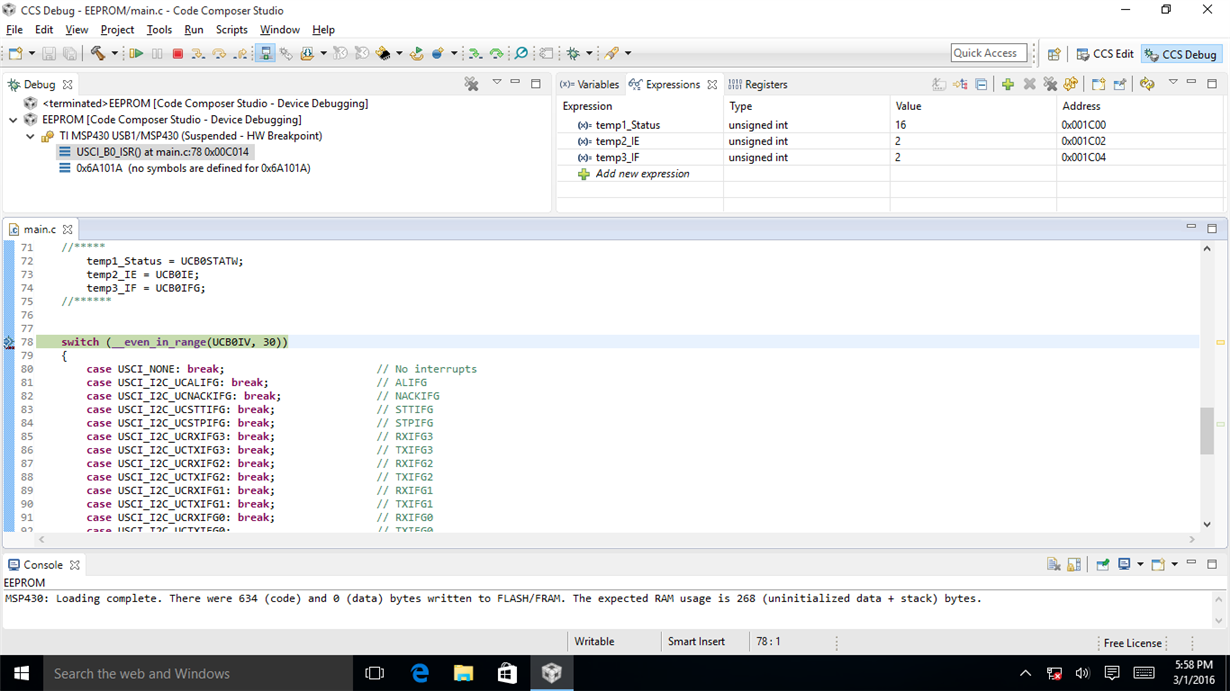

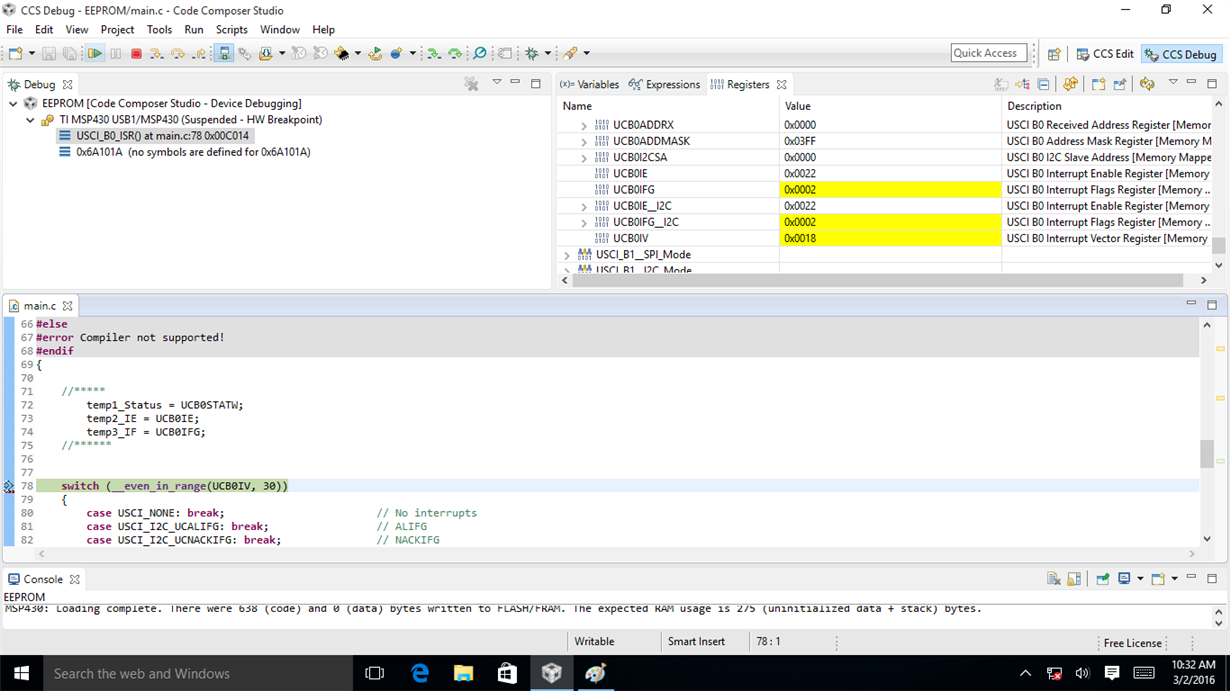

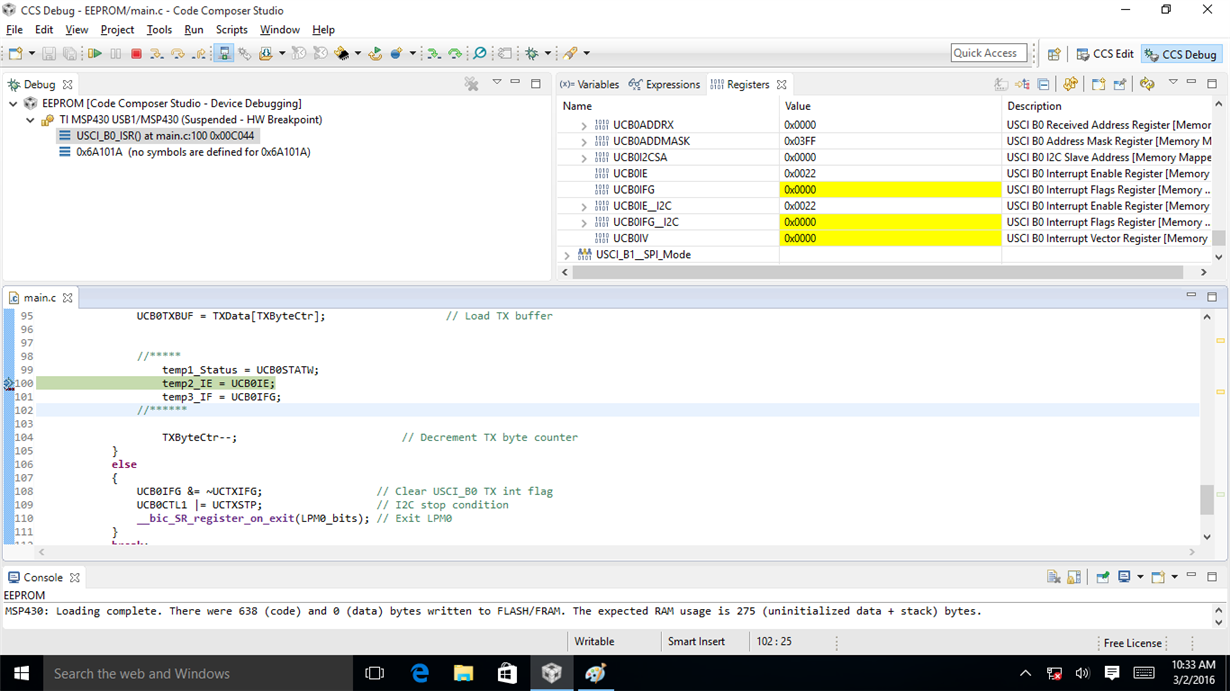

I check interrupt flag register value of I2C which is clear. (00).

Also check Tx buffer value which is clear(00).

and Interrupt enable register (which shows set bit for I2C interrupt.

and If I repeat the I2C start condition generation, then controller going in ISR.

Please guide me.