To whom it may concern,

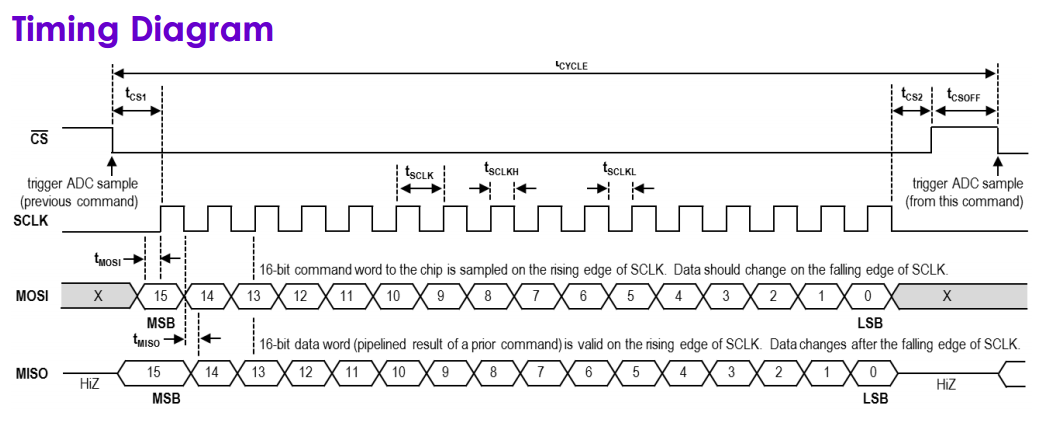

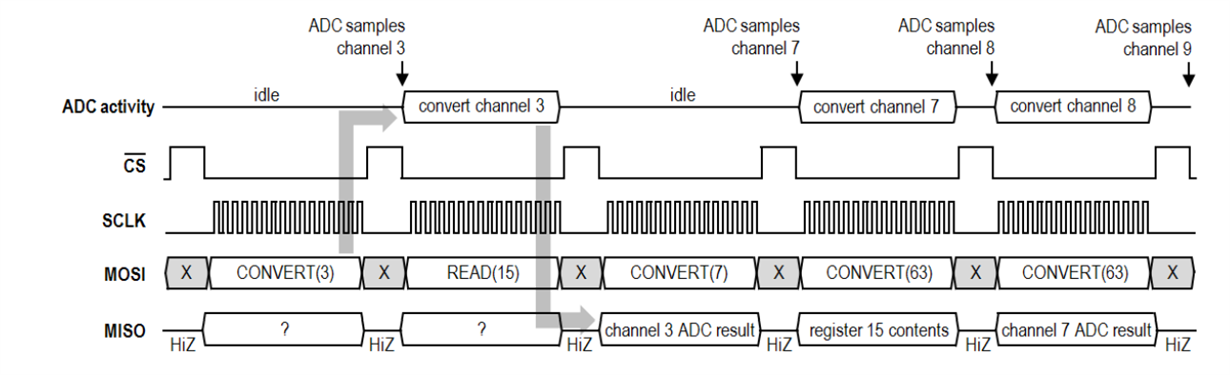

We are doing a project, in which we use a MSP432 microcontroller, with a chip that communicates via SPI.

This chip uses a 16-bit SPI communication and MSP432 is only able to send and receive 8 bits.

We don’t have problem with the transmission by the MSP432, because you can make the MSP432 send 16 bits consecutive.

But the MSP432 isn’t able to receive 16 bits. Because the chip doesn’t give much time to the MSP432 to remove the 8-bit word from the receiver buffer, when the chip is sending the new word (not new for the chip, because this send 16 bits, but new for the MSP432, who is waiting 8 bits).

Thus:

Someone has already implemented a solution to this problem with MSP432?

Someone comes up with a solution to this?

Best Regards,

Santiago.