Hi,

I have practical difficulties to rise SMCKL at 24MHz DCO on MSP432 rev.C to the ratio MCKL/SMCLK = 1:1. I've changed LDO to VCore1 and cleared all dividers. No result: SMCLK = 12 MHz, MCLK=24MHz.

// Switches LDO to VCORE1

while((PCM->CTL1 & PCM_CTL1_PMR_BUSY));

PCM->CTL0 = PCM_CTL0_KEY_VAL | PCM_CTL0_AMR_1;

while((PCM->CTL1 & PCM_CTL1_PMR_BUSY));

CS->KEY = CS_KEY_VAL;

CS->CTL0 = CS_CTL0_DCORSEL_4; // Set DCO to 24MHz

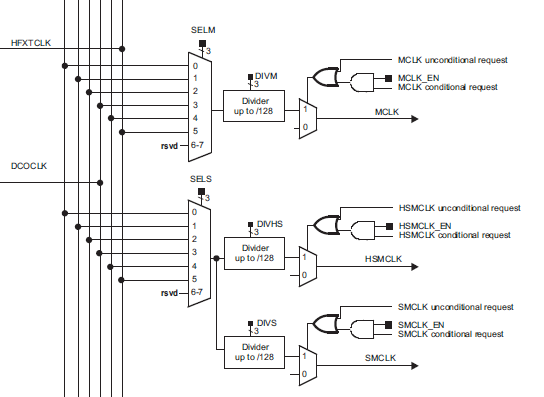

CS->CTL1 = (CS->CTL1 & ~(CS_CTL1_SELM_MASK | CS_CTL1_DIVM_MASK | CS_CTL1_DIVHS_MASK | CS_CTL1_DIVS_MASK | CS_CTL1_SELS_MASK)) | CS_CTL1_SELA__REFOCLK | CS_CTL1_SELS__DCOCLK | CS_CTL1_SELM__DCOCLK;

CS->KEY = 0;

Any ideas why or how to solve it?

Alexey