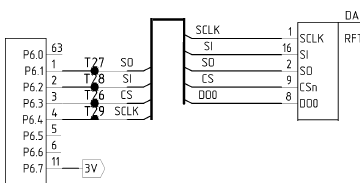

We have a problem with a strange GPIO behavior.

When we change a state of P1.7 output from 1 to 0, a falling glitch occurs on P6.3 output. P6.3 for this case is initialized as an output with a high level.

A voltage drop on P6.3 is so significant, that pin state can be detected as a logical zero in 250 microsecond period.

Also, we have detected, that this issue happens when we use a default setup of microcontroller.

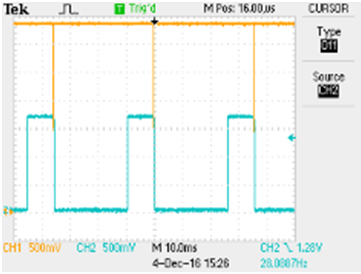

When we use a default setup of micro, the issue is present (img.1).

img.1

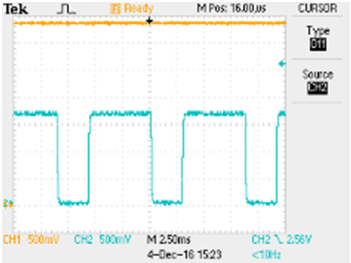

But when we disable a watchdog manually (wich is disabled by default), the issue disappears (img.2).

img.2

We implement a thermostat as described in slaa129b. In our application we use a P1.7 output to control a discharge of external capacitor thru thermoresistor, and P1.6 as a comparator input.

In this case, like in a test programm, we can see a glitch on P6.3 output. We have detected, that duration of glitch varies and depends on time of measurement (time of capacitor discharging) and on thermistor resistance.

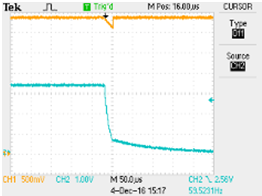

case 1 - thermistor resistance = 1 kOhm (img.3)

img.3

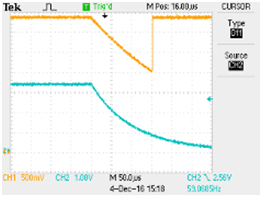

case 2 - thermistor resistance = 10 kOhm (img.4)

img.4

After investigation, we've detected, that problem starts to appear after we switch a comparator ON and enable interrupt from it. manual disabling of WD timer doesn't help in this case.

I can't find such issue in ERRATA.

How can we avoid a voltage glitch on P6.3, and what is the reason of its appearing?