Part Number: MSP430FR5969

Tool/software: Code Composer Studio

Hey , good morning Everyone.

I start to work with drivelib for MSP430FR5969 . I put in my board and in Launchpad xtal 14.7456MHz (535-9839-1-ND Digikey code) with 27pf capacitor.

I selected the SMCLK as output in pin P3.4 ( in my board and in Launchpad.

If I code: CS_initClockSignal ( CS_SMCLK, CS_HFXTCLK_SELECT, CS_CLOCK_DIVIDER_2); The frequency output is 2.4MHZ but the frequency for this xtal need to be 7.3728MHz.

if I code CS_initClockSignal ( CS_SMCLK, CS_DCOCLK_SELECT, CS_CLOCK_DIVIDER_2); with DCOCLK = 8MHZ the frequency output is 4MHZ .

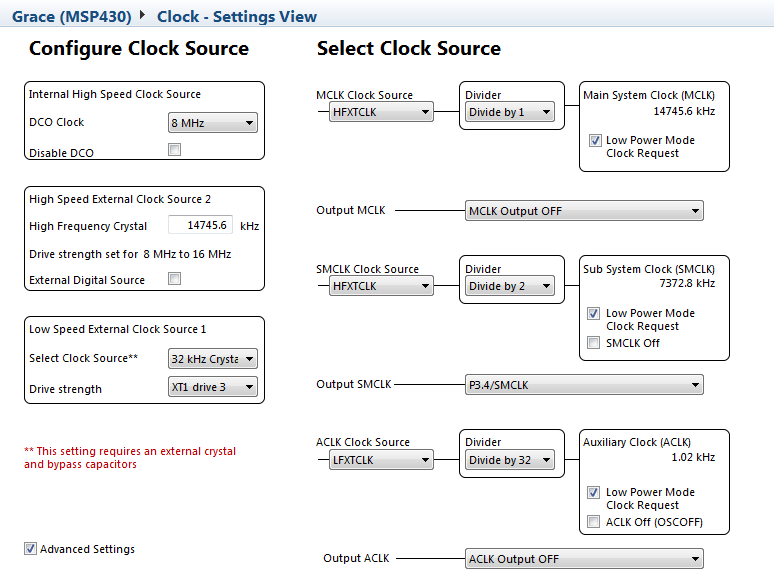

I check all code generated by Grace and is consistent

My code is

void FRCTL_Init(void)

{

FRAMCtl_configureWaitStateControl(FRAMCTL_ACCESS_TIME_CYCLES_1);

}

void Clock_Init(void)

{

/*

* Sets the external clock source for XT1 and XT2. These variables can be used by

* other API functions.

* XT1 Frequency - 32768 Hz

* XT2 Frequency - 14745600 Hz

*/

CS_setExternalClockSource ( 32768, 14745600);

CS_turnOnLFXTWithTimeout(LFXTDRIVE_3, 100000); //Start Low Frequency crystal in low frequency mode

//Start high frequency crystal

//#define CS_HFXT_DRIVE_8MHZ_16MHZ (HFXTDRIVE_1)

CS_turnOnHFXTWithTimeout(HFXTDRIVE_1, 100000);

/*

* Setting MCLK source from CS_HFXTCLK_SELECT with the divider of CS_CLOCK_DIVIDER_1.

*/

CS_initClockSignal (CS_MCLK, CS_HFXTCLK_SELECT, CS_CLOCK_DIVIDER_1);

/*

* Setting SMCLK source from CS_HFXTCLK_SELECT with the divider of CS_CLOCK_DIVIDER_4.

*/

CS_initClockSignal ( CS_SMCLK, CS_HFXTCLK_SELECT, CS_CLOCK_DIVIDER_2); // ( Dont Work)

//CS_initClockSignal ( CS_SMCLK, CS_DCOCLK_SELECT, CS_CLOCK_DIVIDER_2); // (Work)

/*

* Setting ACLK source from CS_LFXTCLK_SELECT with the divider of CS_CLOCK_DIVIDER_32.

*/

CS_initClockSignal (CS_ACLK, CS_LFXTCLK_SELECT, CS_CLOCK_DIVIDER_32);

/*

* Set DCO frequency to 16000000 Hz

*/

CS_setDCOFreq (CS_DCORSEL_0, CS_DCOFSEL_6);

/*

* Clears all oscillator fault flags including global oscillator fault flag

* before switching clock sources

*/

CS_clearAllOscFlagsWithTimeout(100000);

/*

* MCLK clock request enable. Setting this enables conditional module requests for MCLK

*/

CS_disableClockRequest ( CS_MCLK);

/*

* SMCLK clock request enable. Setting this enables conditional module requests for SMCLK

*/

CS_disableClockRequest (CS_SMCLK);

/*

* ACLK clock request enable. Setting this enables conditional module requests for ACLK

*/

CS_disableClockRequest (CS_ACLK);

/* USER CODE START (section: CS_A_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: CS_A_graceInit_epilogue) */

/* Port 3 Port Select Register 1 */

P3SEL1 = BIT4;

/* Port 3 Direction Register */

P3DIR = BIT4;

}