Other Parts Discussed in Thread: MSP-EXP430FR6989

Dear Team,

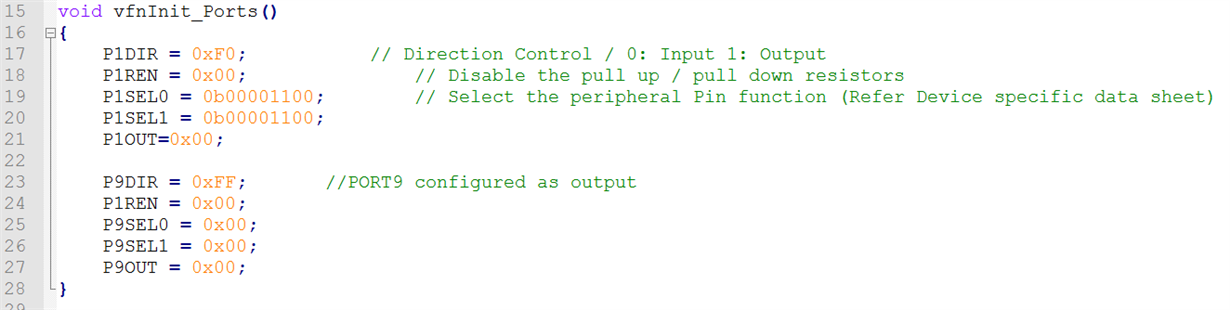

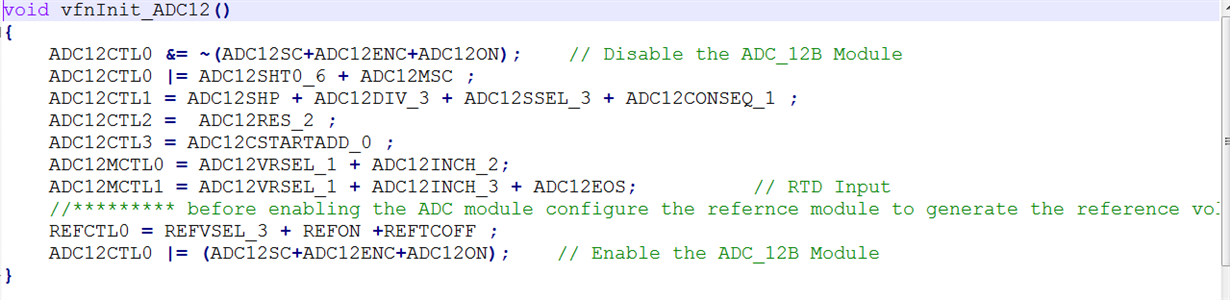

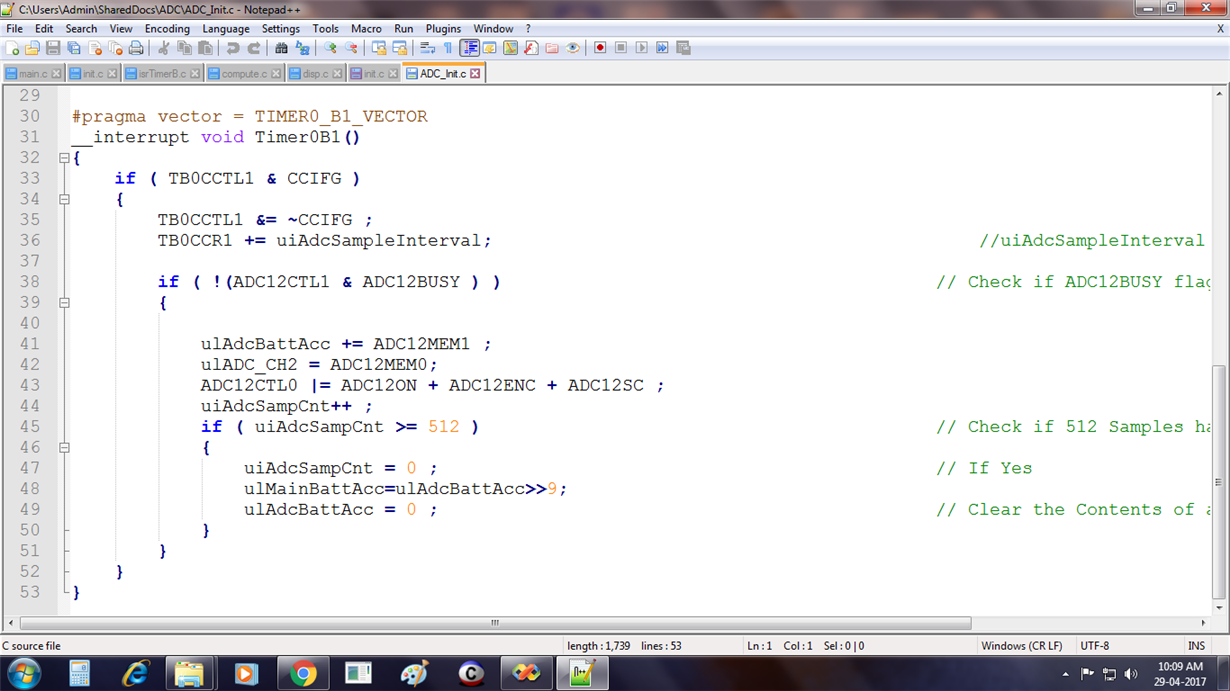

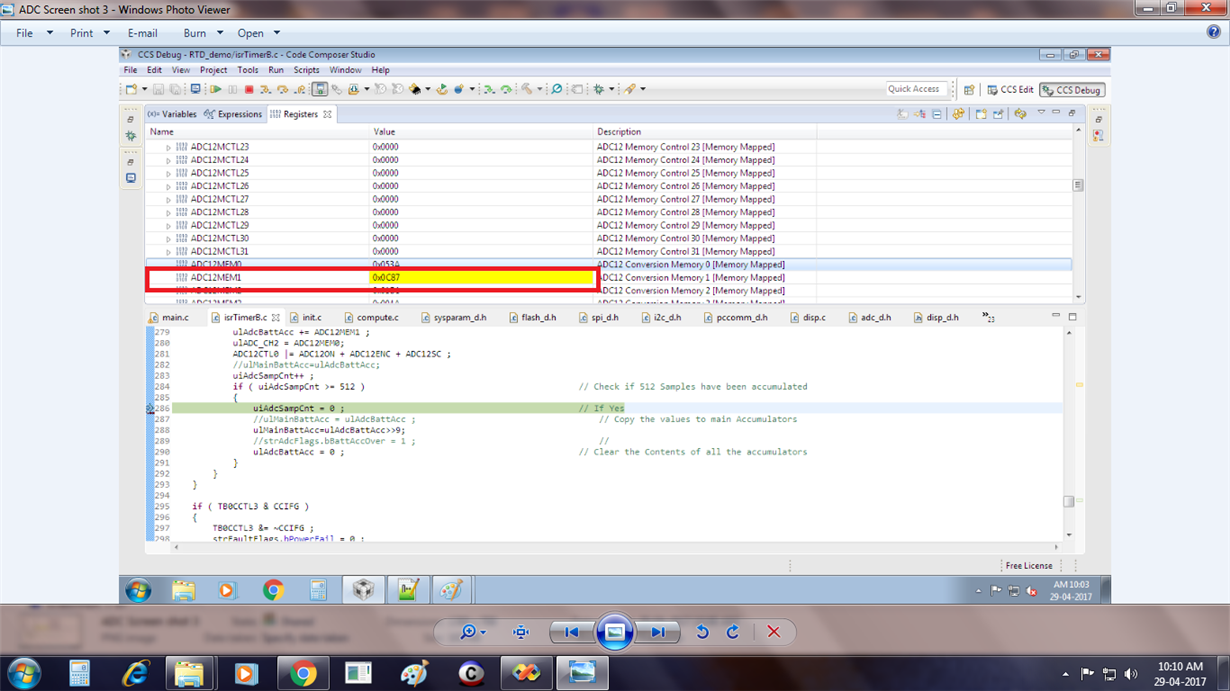

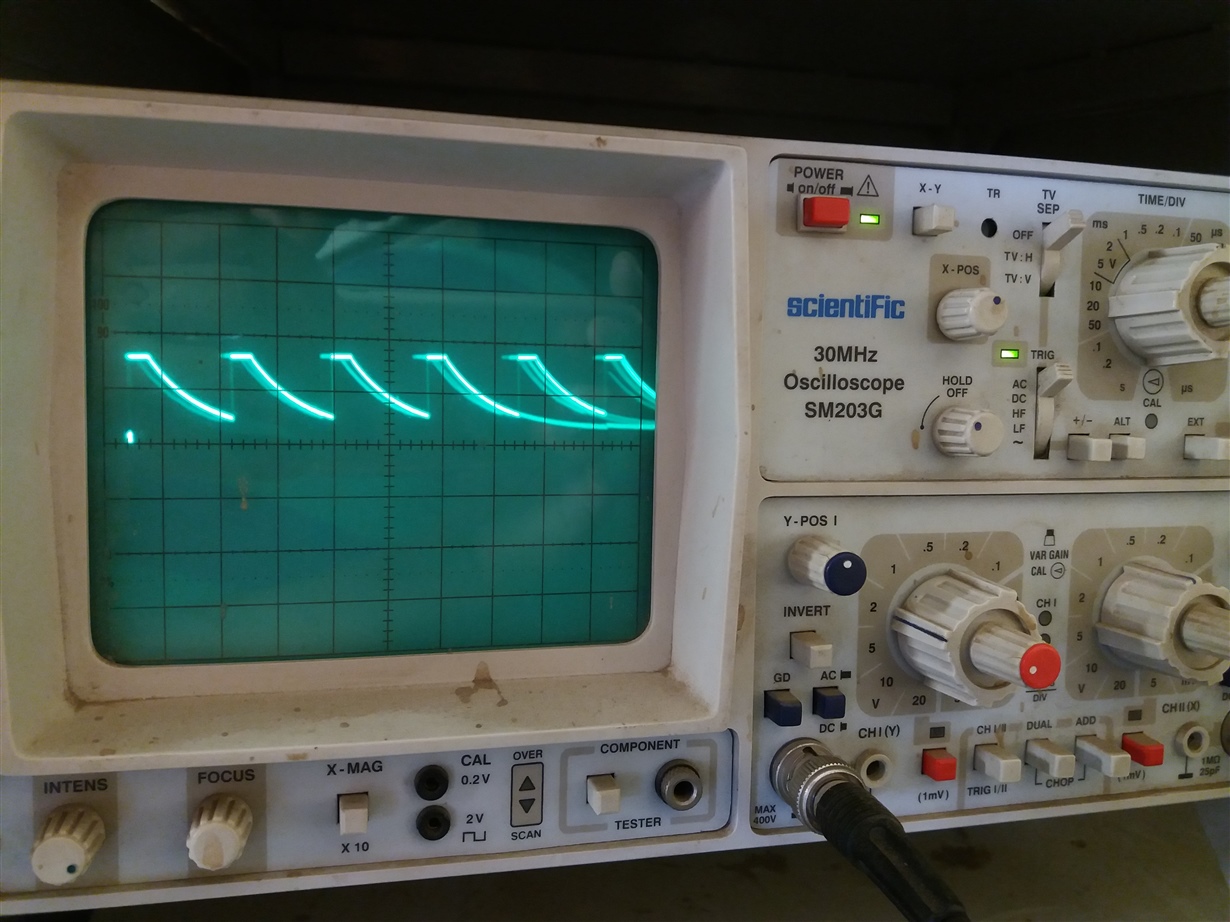

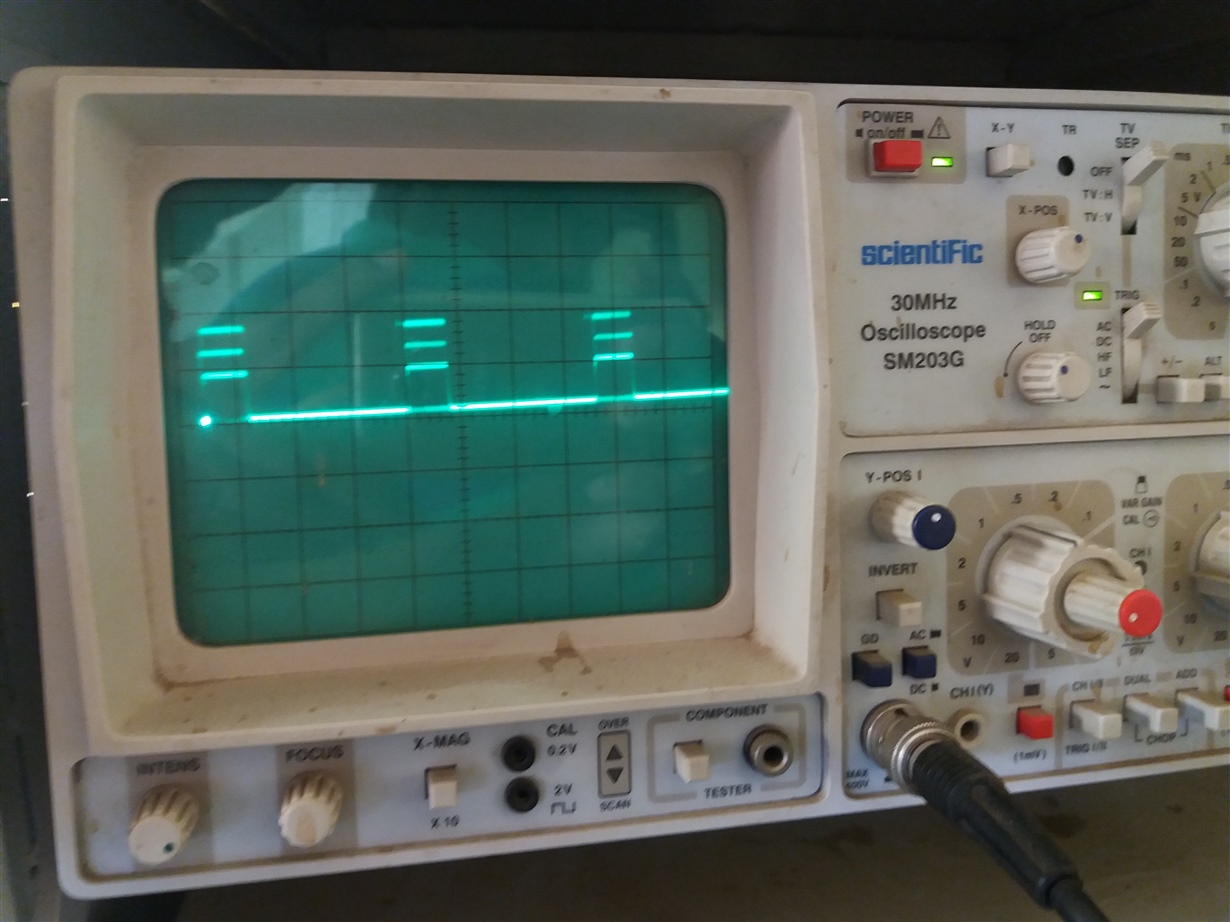

We are facing issue in reading ADC channel A3 (P1.3) in MSP430FR5889 microcontroller. The raw ADC value is varying continuously. But When we changed the P9 output port value to 0x00(i.e P9OUT = 0x00) the reading looks stable. We later noticed that Port 9 is multiplexed with ESI module pins. We have also checked in the debugger the ESI Module register which is to be disabled.

Kindly help us to solve the issue. How would loading 0x00 to Port 9 stabilized the ADC value. ?