Other Parts Discussed in Thread: MSP-EXP430FR5969,

Tool/software: Code Composer Studio

Dear all,

I'm testing SPI interface between MSP430 and the UHF RFID IC Tag SL900A. The problem is that: I cannot write/read data to/from SL900A. And there is a big problem regarding hardware. I don't know why. Please help me in this regard. Thank you so much.

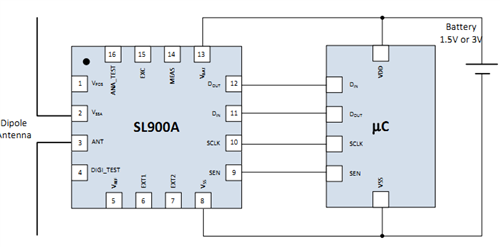

1) Hardware setup:

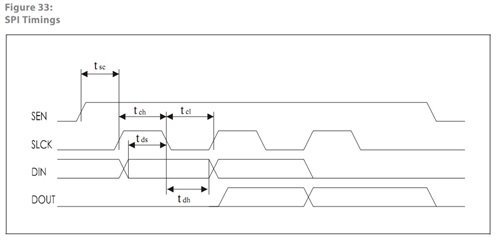

* MSP430: I'm using MSP-EXP430FR5969. and eUSCI_A1 SPI module: P2.4: UCA1CLK (32 kHz); P2.5: UCA1SIMO; P2.6: UCA1SOMI; MCU operates with CLK = 1MHz

* SL900A: as below, except pin 2 is connected to pin 8 (recommended in page 3 datasheet). Battery is 2.5V (but MCU is connected directly to computer through USB, so 2 different Vcc for SL900A & MCU).

2) Coding:

#include <msp430.h>

volatile unsigned char RXData = 0;

volatile unsigned char TXData;

volatile unsigned char var=0;

volatile unsigned int count=0;

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

// Configure GPIO

P2SEL1 |= BIT4; // USCI_A1 operation

P2SEL1 |= BIT5 | BIT6; // USCI_A1 operation

PJSEL0 |= BIT4 | BIT5; // For XT1

P1DIR |= BIT4 + BIT0;

// Disable the GPIO power-on default high-impedance mode to activate

// previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

// XT1 Setup

CSCTL0_H = CSKEY >> 8; // Unlock CS registers

CSCTL1 = DCOFSEL_0; // Set DCO to 1MHz

CSCTL2 = SELA__LFXTCLK | SELS__DCOCLK | SELM__DCOCLK;

CSCTL3 = DIVA__1 | DIVS__1 | DIVM__1; // set all dividers

CSCTL4 &= ~LFXTOFF;

do

{

CSCTL5 &= ~LFXTOFFG; // Clear XT1 fault flag

SFRIFG1 &= ~OFIFG;

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

CSCTL0_H = 0; // Lock CS registers

// Configure USCI_A0 for SPI operation

UCA1CTLW0 = UCSWRST; // **Put state machine in reset**

UCA1CTLW0 |= UCMST | UCSYNC | UCMSB; // 3-pin, 8-bit SPI master, MSB first

// Clock polarity: data changed with first low-to-high transition of CLK

UCA1CTLW0 |= UCSSEL__ACLK; // ACLK

UCA1BR0 = 0x00; // fclk = 32kHz

UCA1BR1 = 0; //

UCA1MCTLW = 0; // No modulation

UCA1CTLW0 &= ~UCSWRST; // **Initialize USCI state machine**

//UCA1IE |= UCRXIE; // Enable USCI_A0 RX interrupt

P1OUT |= BIT4; // SEN is enabled

_delay_cycles(200);

while(1)

{

UCA1IE |= UCTXIE;

__bis_SR_register(LPM0_bits | GIE); // CPU off, enable interrupts

__delay_cycles(2000); // Delay before next transmission

P1OUT ^= BIT0;

}

}

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=USCI_A1_VECTOR

__interrupt void USCI_A1_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_A1_VECTOR))) USCI_A1_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(UCA1IV, USCI_SPI_UCTXIFG))

{

case USCI_NONE: break;

case USCI_SPI_UCRXIFG:

RXData = UCA1RXBUF;

UCA1IFG &= ~UCRXIFG;

__bic_SR_register_on_exit(LPM0_bits); // Wake up to setup next TX

break;

case USCI_SPI_UCTXIFG:

count++;

if (var==0) {

TXData = 0;

UCA1TXBUF = TXData; // Transmit characters

var++;

}

else if (var ==1) {

TXData = 0x64;

UCA1TXBUF = TXData; // Transmit characters

var++;

}

else if (var == 2) {

TXData = 0x55;

UCA1TXBUF = TXData; // Transmit characters

var++;

}

UCA1IE &= ~UCTXIE;

__bic_SR_register_on_exit(LPM0_bits); // Wake up to setup next TX

break;

default: break;

}

}

3) Problems:

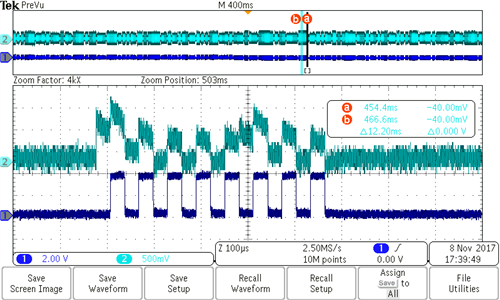

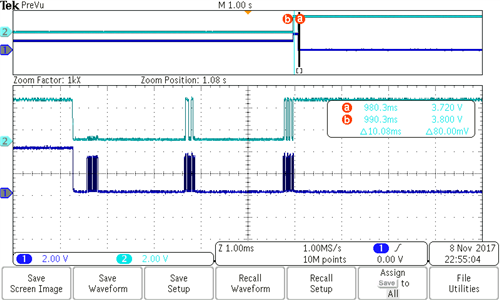

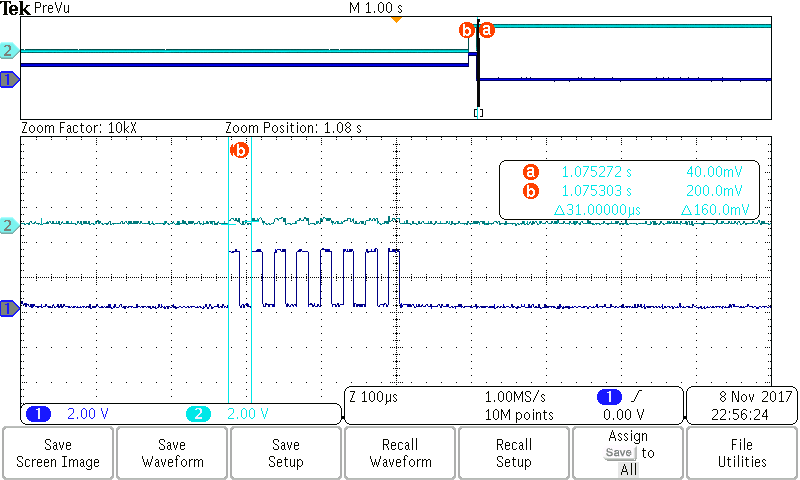

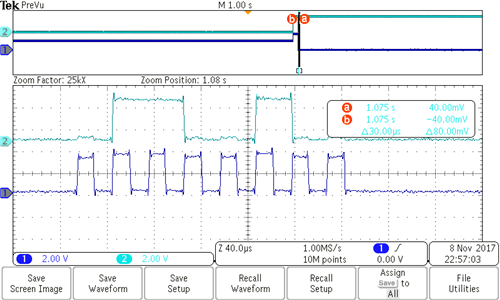

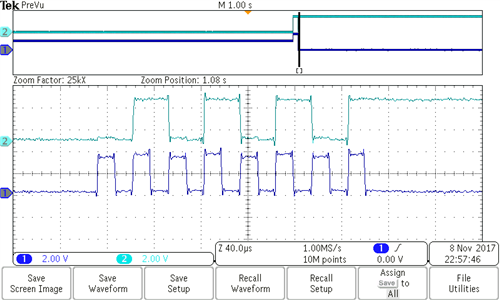

* Reading: when I tried to read data from FIFO (using Direct Command), I got only noise. Please see the pic below, when (1): SPI CLK, (2): P2.6 (UCA1SOMI). One more thing: I had to disconnect GND between SL900A and MCU. If their GNDs were connected, I got NO CLK (only spike instead of bit0-1).

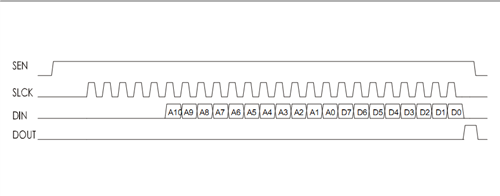

* Writing: I tried to write data (0x55) into User's Memory of SL900A, started at addr of 0x064. These are 3 bytes I wrote to SL900A. But then, the data were all 0 when I read User Memory from reader (RFID interface).

(1): SPI CLK; (2): P2.5 (UCA1SIMO)

Byte 1: 0x00 (Write Command)

Byte 2: 0x64 (Address of SL900A EEPROM)

Byte 3: 0x55 (Data to be written)

I'm so confused. Please help me explain these things. Thank you so much.