Tool/software: Code Composer Studio

Hi :

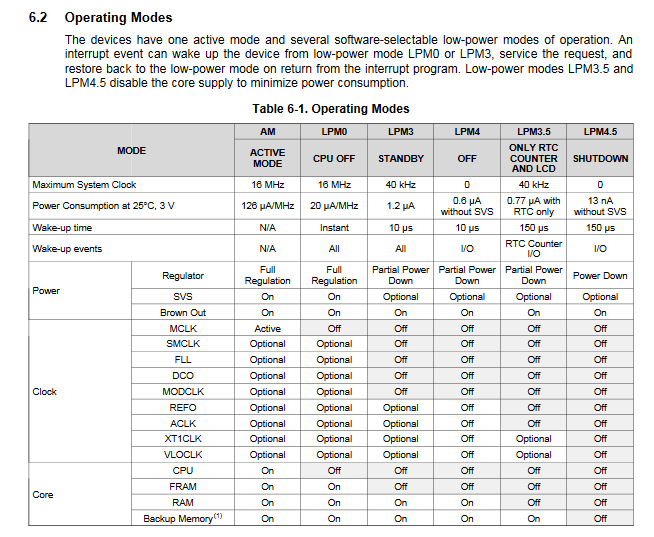

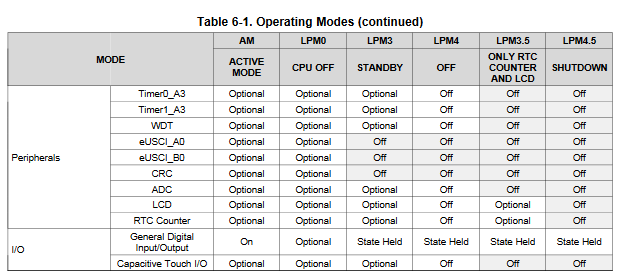

We can see that MODCLK is closed in LPM3 in MSP430FR4133 Datasheet as below:

But when I used the ADC with MOKCLK in LPM3(with MSP430FR4133 LaunchPad), the ADC can also work(I changed the input voltage and the ADC result follow changed)! I used the RTC to start the ADC sampling and conversion (do not wake up CPU).

What's more there are about two or three cycles of SMCLK when the ADC started. The test code is attached.

paper_msp430fr413x_window.c.zip

Best regards

Gary Gao