Hello Champs,

One of my customer is developing msp430 application using F6775.

Recently they shwon the lockup issue at the power off-> on test.

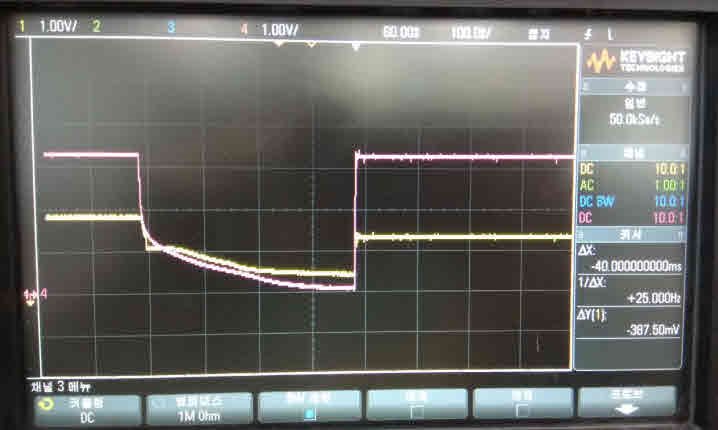

When decreasing voltage level at the power off state, their system shows the Vcore is higher than DVCC as shown below image.

<Red color : DVCC, Yellow color : Vcore, 1V/div>

If they power on when Vcore > DVCC and DVCC > 1.4V, MCU does not work properly.

Do you know any reason for that?

Note that, if they change C_Vcore from 470nF to 22nF, then it can't be Vcore > DVCC condition, then it work as normal reset.

Please see the schematic for your reference too.

Best Regards,

Ernest