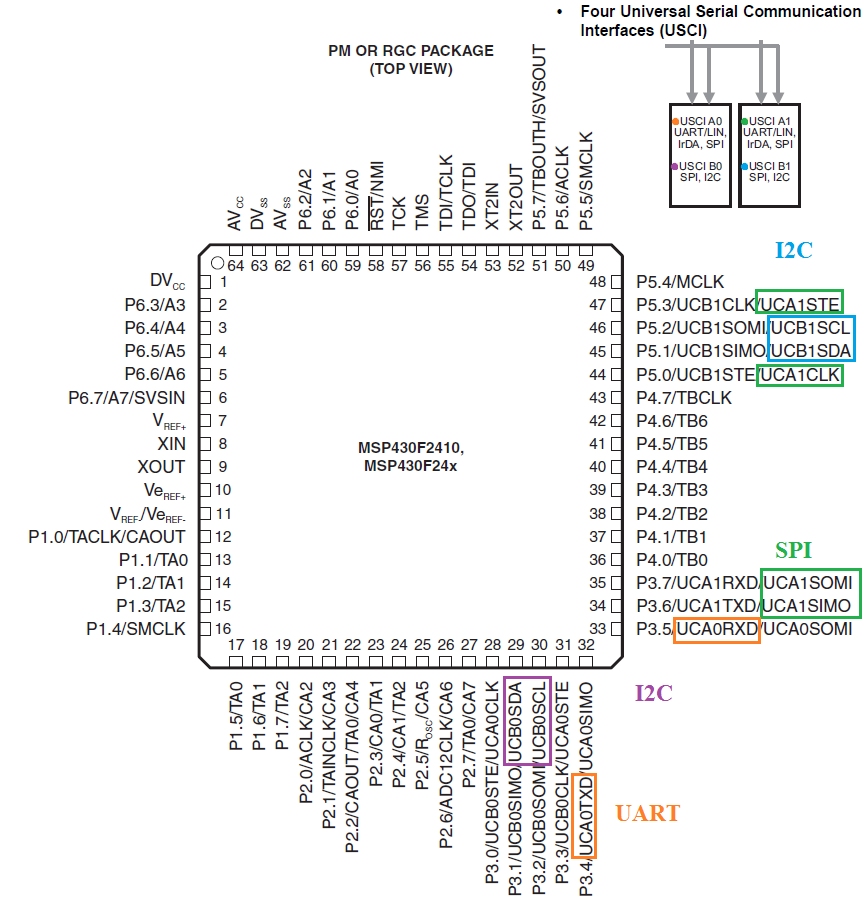

I am trying to confirm the possibility of assigning the following USCI's interfaces in a proposed application on a single MSP430F247: two I2C, one SPI and one UART interfaces. The colored picture below is self explanatory.I am using the MSP430F247 as an example but this is really about TI's hardware convention not just that IC. So yes, I scrutinized the datasheet and the specific user guide carefully. I have 90% confidence that this is not violating any hardware partitioning in the MSP but one of the diagram in the datasheet cast a shadow of doubt. I reproduced it on the top right of my picture below for convenience. It shows two boxes : ( USCI A0 + USCi B0 ) in one box and ( USCI A1 + USCi B1 ) in a second box. Is this apparent partitioning indicative of a hardware limitation ?

The proposed four interfaces don't seem to have any pin assignment issue and the register map addresses do not clash either. Finally the datasheet says 4 interfaces (but in which logical OR/AND configuration ?). Better be 100% sure than having to redo a board design.