Tool/software: Code Composer Studio

Hallo,

at the 20pin-version I have to move a PWM signal from TA1.1 to TA0.1 to get TA1 available for other purpose (ADC-triggering). Since both timers are of type A I do the same thing at all registers TA0xyz that I'd successfully done with TA1xyz before. The pin configuration, however is different:

TA1.1 used pin 13 with P2SELx=01b and P2DIR.x=1

TA0.1 shall use pin 17 with P2SELx=10b and P1Dir.x=1

Configuring UCA0TXD instead of TA0.1 for this pin also does not work. However, configuring P1.4-IO instead of TA0.1 for this pin works fine!!!

Reading the counter value TA0R shows that the counter is running. It is only the pin which seams to fail when configured for TA0.1.

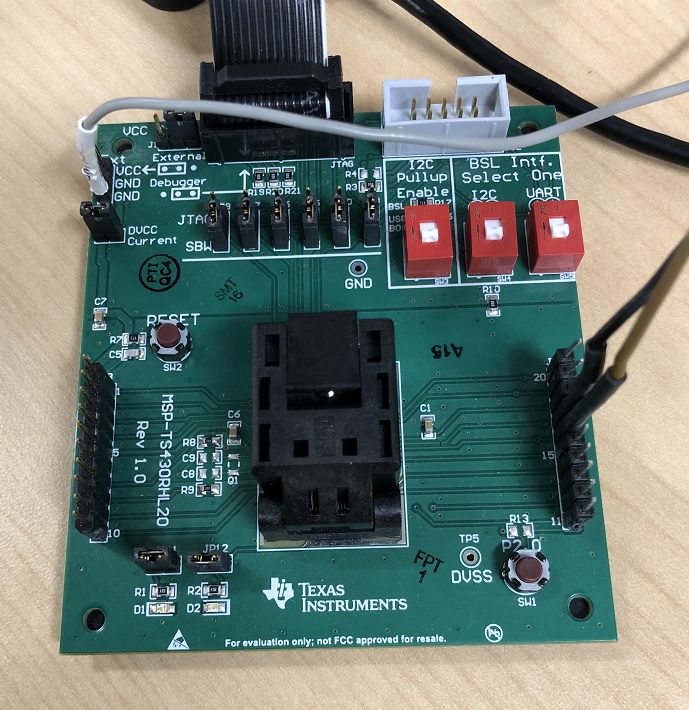

I use the evaluation board MSP-TS430-RHL20 with all jumpers (JP5 - JP10) set to SBW and SW3 - SW5 set to OFF. Flashing and debuggigs works well.

By the way TA0.1 at pin 16 as document SLASEE5A (data sheet) tells seams to be wrong, but pin 17 as document SLAU278AE (Hardware Tools User's Guide) tells seams to be correct. I conclude this since P1.4 works at pin 17. Anyway I checked both pins.

Is there any idea what else to consider to let the signal out of pin 17?

Best regards

Stefan