Other Parts Discussed in Thread: MSP430F169, MSP430FR2422

Hello ...

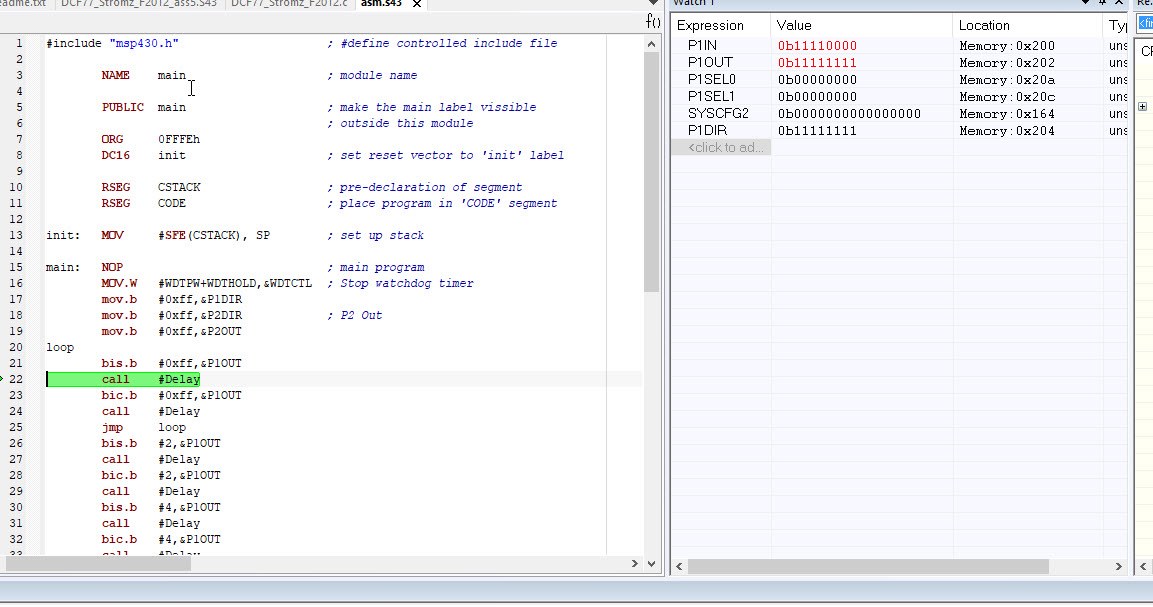

I have a further Question. In my MSP430F2012 I have programmed a I2C Slave Application. At the I2C Bus are more Devices connected. When the master prompts a slave for Data transfer, after the Transfer the 2012-Slave is always in I2C-Interrupts. No action can stop this Interrupts and the program is in endless loop. What can I do to stop the endless loop. I have used an Example from Ti: msp430x20x3_usi_09.s43.

Regards Jurgen