Other Parts Discussed in Thread: UNIFLASH, , MSP430FR6989

Hi,

My customer reported strange behavior with Uniflash and MSP430FR6879.

They are testing their product with below sequence.

1) Write program with Uniflash

2) Verification is OK

3) Perform a several functional tests and all tests are passed.

4) Power cycle the device (power-off, then power-up again).

5) Verify again with Uniflah => verification fails with *some* devices

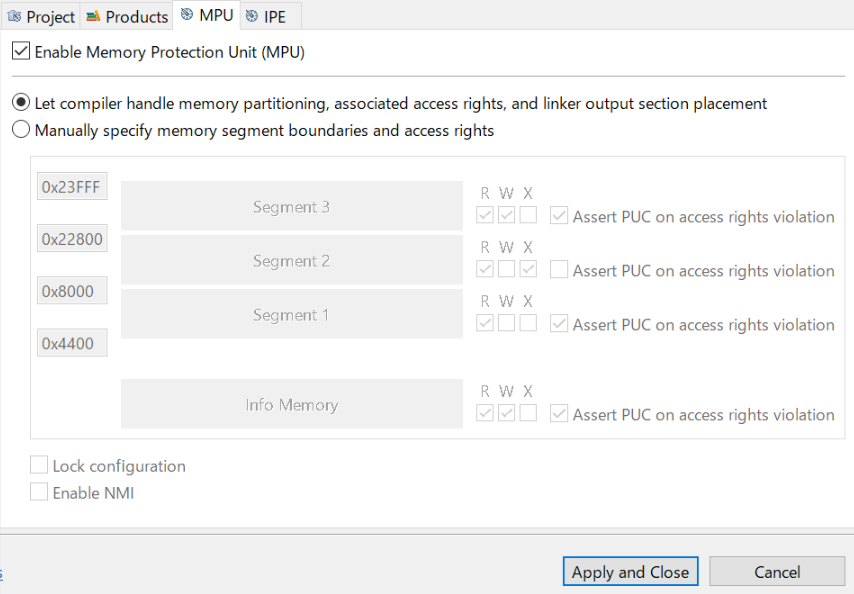

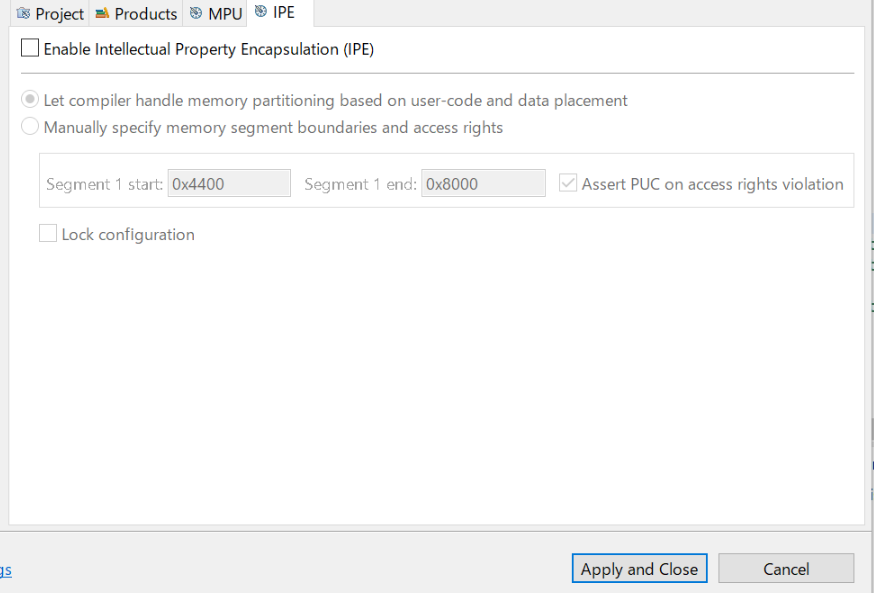

The error addresses are different by board, but the addresses are all inside MPU protected area.

Board#40:

[2019/5/28 13:45:43] [ERROR] MSP430: File Loader: Verification failed: Values at address 0x0D558 do not match Please verify target memory and memory map.

Board#24:

[2019/5/28 13:57:33] [ERROR] MSP430: File Loader: Verification failed: Values at address 0x0D7EC do not match Please verify target memory and memory map.

Board#42:

[2019/5/28 13:39:08] [ERROR] MSP430: File Loader: Verification failed: Values at address 0x0D7F6 do not match Please verify target memory and memory map.

Board#63:

[2019/5/28 13:51:44] [ERROR] MSP430: File Loader: Verification failed: Values at address 0x0C832 do not match Please verify target memory and memory map.

Board#22:

[2019/5/28 14:15:09] [ERROR] MSP430: File Loader: Verification failed: Values at address 0x0AE34 do not match Please verify target memory and memory map.

With the same board, always the same address is failed. For example, Board#40 always fails at 0x0D558.

Is this related to MPU function? There are many other boards which are not failing with exactly the same procedure.

Any possible cause of such issue?

Thanks and regards,

Koichiro Tashiro