TWIMC,

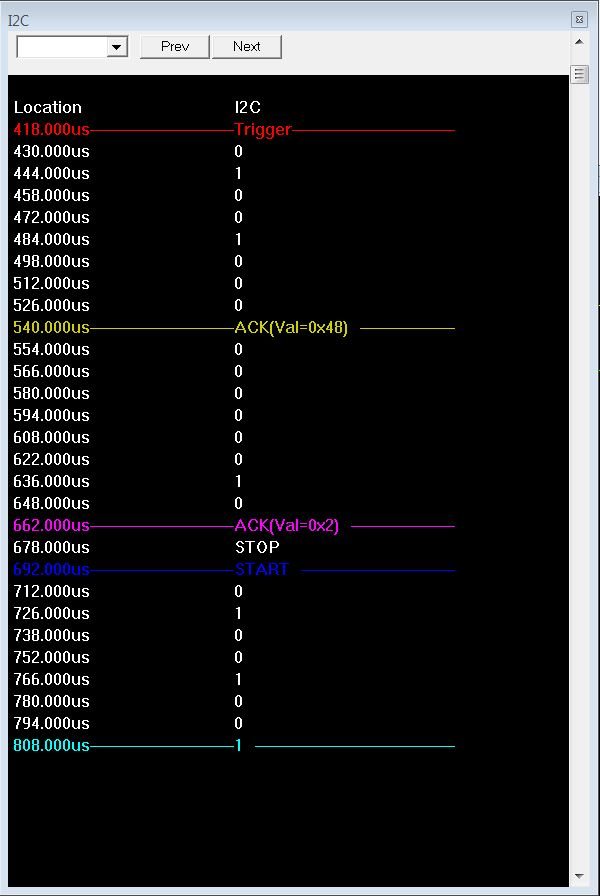

I am programming an I2C slave to respond to Master I2C requests. The transactions from the master are an I2C write sequence to transmit the register address in the MSP430 to read, followed by a repeated start condition (Stop+Start) and a read transaction to read two bytes of data to read a 16-bit register. What I am seeing per the screenshots below (with a known good working master) is that the I2C slave is not ACK'ing the secondary read address after the repeated start condition even though it properly ACK'd the first address transaction during the earlier write phase of the transaction. Scope plots and I2C decode records attached below.

What can cause the I2C slave from generating the ACK on the second half of the transaction during the read portion of the exchange?