Other Parts Discussed in Thread: MSP430F249

Tool/software: Code Composer Studio

Gentlemen,

TMS430F249 was not accepted in the Part Number field above???

I am attempting to set up Timer A0 as an up counter to 480 but the CPU never gets to the ISR. It traps to:

;******************************************************************************

;* ISR_TRAP.ASM - *

;* *

;* Copyright (c) 2003 Texas Instruments Incorporated *

;* http://www.ti.com/ *

;* *

;* Redistribution and use in source and binary forms, with or without *

;* modification, are permitted provided that the following conditions *

;* are met: *

;* *

;* Redistributions of source code must retain the above copyright *

;* notice, this list of conditions and the following disclaimer. *

;* *

;* Redistributions in binary form must reproduce the above copyright *

;* notice, this list of conditions and the following disclaimer in *

;* the documentation and/or other materials provided with the *

;* distribution. *

;* *

;* Neither the name of Texas Instruments Incorporated nor the names *

;* of its contributors may be used to endorse or promote products *

;* derived from this software without specific prior written *

;* permission. *

;* *

;* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS *

;* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT *

;* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR *

;* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT *

;* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, *

;* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT *

;* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, *

;* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY *

;* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT *

;* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE *

;* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. *

;* *

;******************************************************************************

;-----------------------------------------------------------------------------

;-- default ISR handler if user does not supply

;-- simply puts device into lpm0

;-----------------------------------------------------------------------------

.sect ".text:_isr:__TI_ISR_TRAP"

.align 2

.global __TI_ISR_TRAP

__TI_ISR_TRAP:

BIS.W #(0x0010),SR

JMP __TI_ISR_TRAP

NOP ; CPU40 Compatibility NOP

My setup:

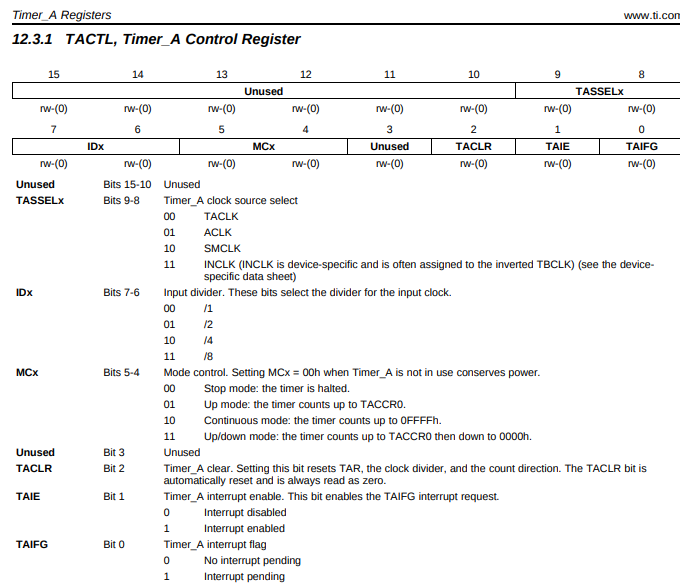

// Timer A0 Initialization.

TACTL = MC_0; // Shut down Timer A0.

TACTL = TASSEL_1; // Select ACLK as clock source and divide by 1.

TACCR0 = 480; // Set compare register for ~ 30 usec.

TACTL |= TAIE; // Timer A interrupt enable.

TACTL |= MC_1; // Set timer A to up counting mode.

My ISR:

/*********************************************************************************************

* NAME: evTMR_A0_isr

*

* DESCRIPTION: Timer A0 interrupt processor.

* Read the next byte from the C3_PM.

* SMBus_Buffer - each byte from the C3 is built bit by bit in this memory location.

* The timer A0 interrupt flag is also cleared just prior to exit.

*

*********************************************************************************************/

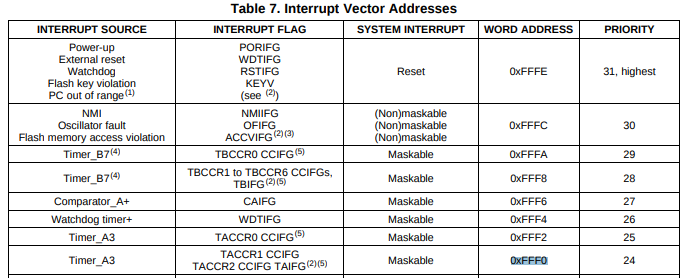

#pragma vector = TIMERA0_VECTOR

__interrupt void evTMR_A0_isr(void)

{

// Scope trigger

P1OUT &= ~M_LED4; // Turn on M_LED4.

if( C3_BYTE_READ == ( C3_BYTE_READ & SMBus_Flags ) ) {

Port_Five_Snapshot = P5IN; // Snapshot of SMBus comm port with the C3_PM Card.

switch(C3_Byte_Rd_State) // ***** Beginning of C3 Byte Read State Machine *****

{

case C3_Byte_Init:

if( nM_SCL & ~Port_Five_Snapshot ) { // If the clock line has gone low then...

bit_position = 8; // Initialze the bit counter.

C3_Byte_Rd_State = C3_Byte_Wait1;

}

break;

case C3_Byte_Wait1:

if( nM_SCL & Port_Five_Snapshot ) { // If valid data bit has been sent...

if(nM_SDA & Port_Five_Snapshot) { SMBus_Buffer |= 0x01; } // If SMBdata is a 1, OR a 1 into data byte LSB...

else { SMBus_Buffer &= 0xFE; } // otherwise clear the LSB.

bit_position--; // Decrement the bit count.

C3_Byte_Rd_State = C3_Byte_Wait2;

}

break;

case C3_Byte_Wait2: // Wait here for the clock line to go low.

if( nM_SCL & ~Port_Five_Snapshot ) {

if(bit_position > 0 ) { // If there are more bits in the byte to collect then...

SMBus_Buffer <<= 1; // Shift the bit just received toward the MSbit.

C3_Byte_Rd_State = C3_Byte_Wait1; // Go read the next bit.

}

// Acknowledge receipt of the last data bit. Pull data line low.

else{

SMBdata_Clr_C3;

C3_Byte_Rd_State = C3_Byte_Ack1; }

}

break;

case C3_Byte_Ack1: // Wait for the SMBus clock to go high.

if( nM_SCL & Port_Five_Snapshot ) {

C3_Byte_Rd_State = C3_Byte_Ack2;

}

break;

case C3_Byte_Ack2: // Wait for the SMBus clock to go low to complete the acknowledge.

if( nM_SCL & ~Port_Five_Snapshot ) { // If clock has gone low, terminate acknowledge.

SMBdata_Set_C3; // Release the SMBus data line to be pulled high.

SMBus_Flags &= ~C3_BYTE_READ; // Shut down the C3 Card byte read state machine.

C3_Byte_Rd_State = C3_Byte_Init; // Rearm state machine.

}

break;

} // Endcase C3 Card byte read.

} // Endif C3_BYTE_READ

// ????? TAIFG &= ~BIT0; // Clear the interrupt flag.

TA0R = 0; // Restart counter.

// Scope trigger

P1OUT |= M_LED4; // Turn off M_LED4.

}

Please advise.

Regards, Harvey Novak