For the following code, I expect to get SIMO that gives 8 bits of 0x0F, then 8 bits of 0x5F.

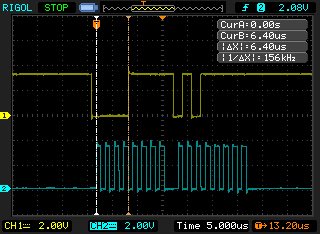

Instead I get 8 bits of 0x09 followed by 8 bits of 0x00. See scope traces below where top trace is SCLK and bottom trace is SIMO.

What is wrong with the code?

I put the SPI writes in a loop so I can capture easier on the scope; usually I would only write once to each address.

#include <msp430.h>

int main(void)

{

volatile unsigned int i;

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer

P1DIR |= BIT0 + +BIT2 + BIT3 + BIT4 ; // nCS_BD, nRST_BD, SIMO, SCLK are outputs

P2DIR |= BIT6 ; // nPWM1_BD are outputs

P1SEL = BIT1 + BIT2 + BIT4; // SOMI, SIMO SCLK are SPI

P1SEL2 = BIT1 + BIT2 + BIT4; // ditto

P2SEL &= ~BIT6; // Make P2.6 (nPWM1_BD) so it is not XIN

UCA0CTL0 |= UCSWRST; // eUSCI logic held in reset state

UCA0CTL0 |= UCMSB+UCMST+UCSYNC+ UCCKPH; // 3-pin, 8-bit SPI master PH=1, PL=0

UCA0CTL1 |= UCSSEL_2; // SMCLK

UCA0BR0 |= 0x02; // /2

UCA0BR1 = 0; // Bit clock prescaler setting

UCA0MCTL = 0; // No modulation

UCA0CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

P1OUT |= BIT3; // nRST_BD to high (BD not in reset)

while (1){

P1OUT &= ~BIT0; // Set nSCS_BD low

__delay_cycles(10);

UCA0TXBUF = 0x0F; // Transmit address 0x0F (BD enable register)

while (!(IFG2 & UCA0TXIFG)); // Wait until the TX buffer is done

//__delay_cycles(10);

UCA0TXBUF = 0x5F; // Transmit data 0x5F is enable all

while (!(IFG2 & UCA0TXIFG)); // Wait for the TX buffer

__delay_cycles(10);

P1OUT |= BIT0; // Set nSCS_DRV high

__delay_cycles(10);

}

}