Tool/software: Code Composer Studio

We are using this very simple SPI code to write to a DAC but the DAC output does not change.

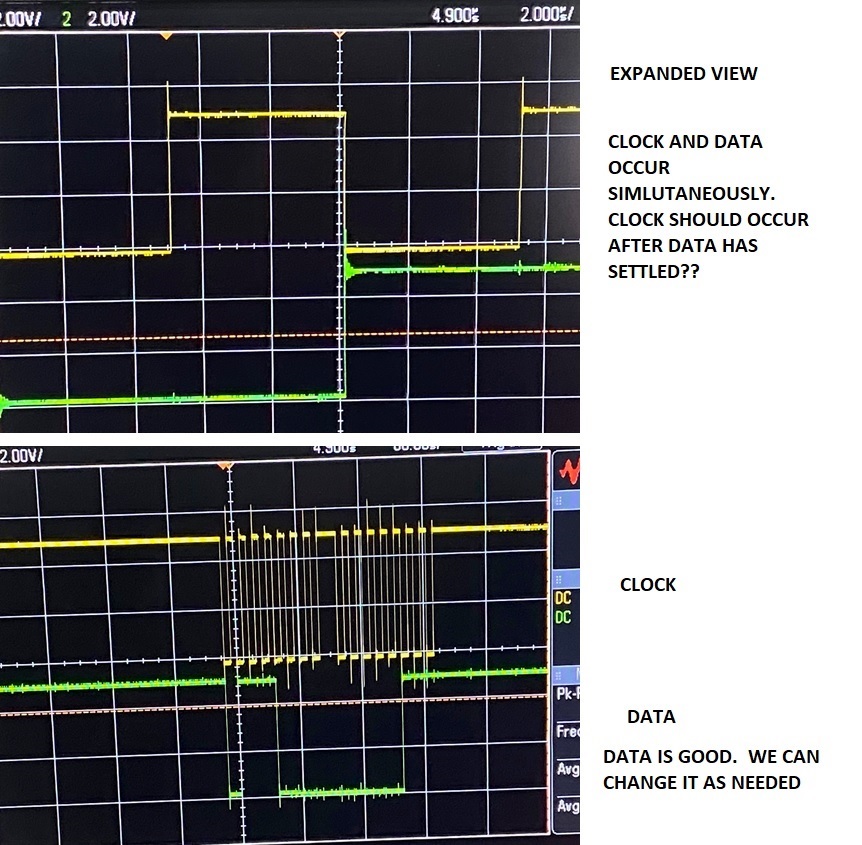

The attached Clock and Data trace show that the clock and data transition are at the exact same instant. No 4ns delay so DAC may be reading garbage. The clock - data lines have a slight delay in all of the spec sheets but not on the trace.

HOW CAN WE DELAY THE CLOCK SO THE DATA CAN SETTLE? Is this the likely problem?

Thanks, Peter

________________________________________________________

#include "main.h"

unsigned int data16,datahi,datalo;

int spi_init (void)

{

P3SEL |= BIT1; // P3.1 UCB0SIMO (Slave in, master out – USCI_B0 SPI mode)

P3SEL |= BIT2; // P3.2 UCB0SOMI (Slave out, master in – USCI_B0 SPI mode)

P3SEL |= BIT3; // P3.3 UCB0CLK (Clock in\out)

IO_OUTPUT(P3,BIT0); //p3.0 CS output

UCB0CTL1 |= UCSWRST; // Put state machine in reset**

UCB0CTL0 |= UCMST+UCSYNC+UCCKPL+UCMSB; // 3-pin, 8-bit SPI master, Clock polarity high, MSB

//UCB0CTL0 |= UCCKPH + UCMSB + UCMST + UCSYNC; // we played with the phase and polarity of clock but not better

UCB0CTL1 |= UCSSEL_2; // SMCLK

//UCB0BR0 = 0x02; // /2 SMCLK=5.2MHZ if div=2 then clock is 2.4Mhz TOO FAST!

UCB0BR0 = 52; // SMCLK=5.2MHZ div=5.2mhz/100,000=52 BR0+BR1x256 so make div=52 for 100K clock

UCB0BR1 = 0;

UCB0CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

return 0;

}

/*************************************************************************************/

#define SPI_HDR 0x7000 //0011 bit 16 =0 write bit 15 1=buffered bit 14 GA=1=vref*D/4096 bit 13 SHDC=1

int spi_tx (int spi12bit) { int i;

spi12bit = spi12bit & 0xFFF; //get 12 bits

data16 = SPI_HDR + spi12bit; //MCP4921 header + data

datahi=data16>>8; datalo=data16 & 0xFF;

IO_LOW(P3,BIT0); for(i=0;i<20;i++); //chip select low. wait

UCB0TXBUF = datahi;

while (UCB0STAT & UCBUSY); //wait for finish

UCB0TXBUF = datalo;

while (UCB0STAT & UCBUSY); //wait for finish

for(i=0;i<20;i++); IO_HIGH(P3,BIT0); //chip select high

return 0;

}