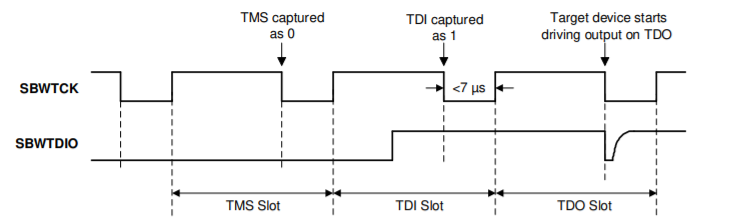

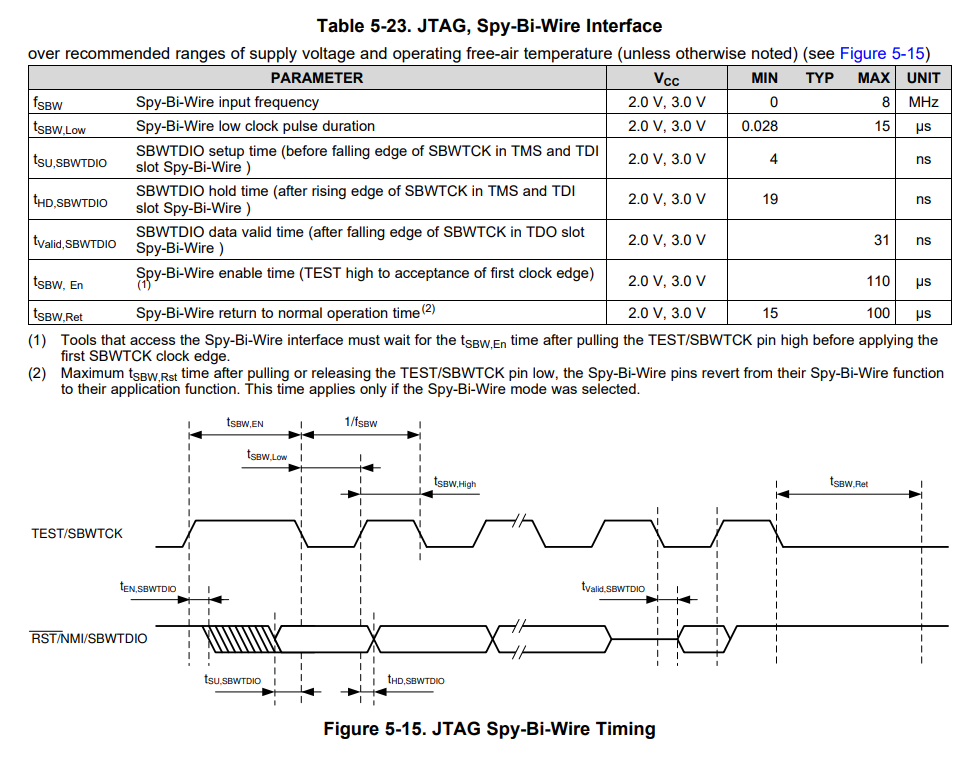

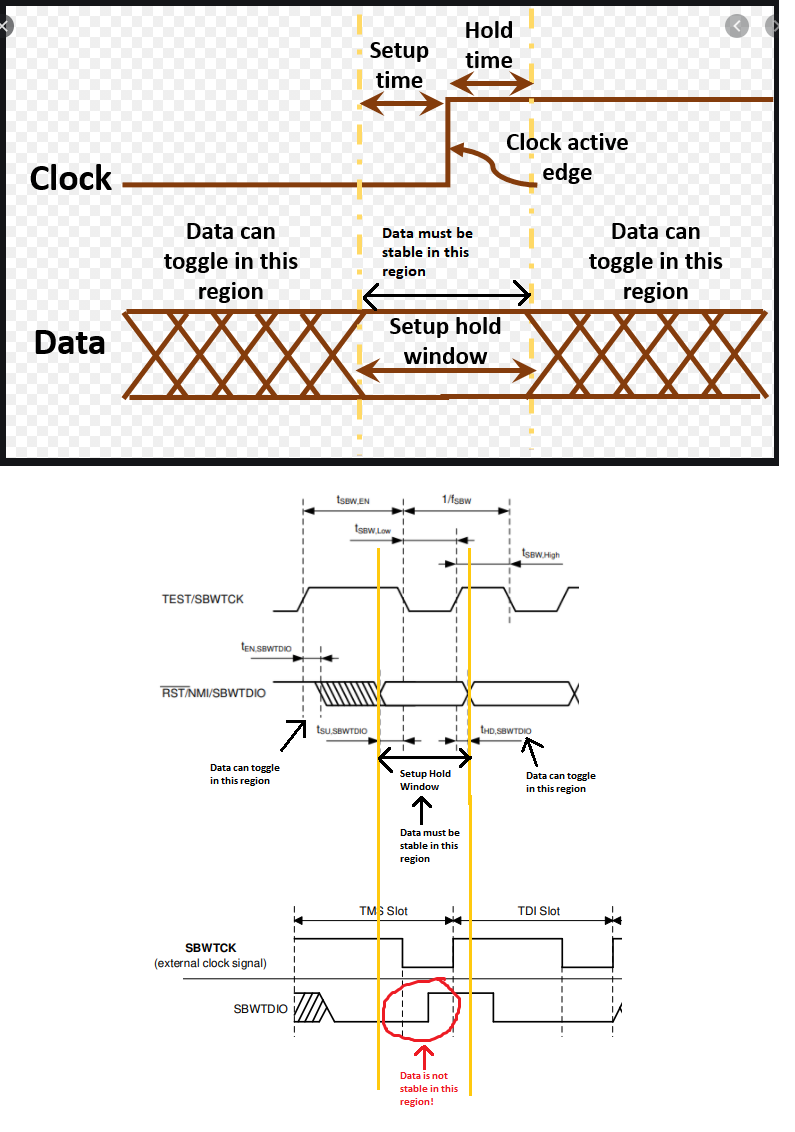

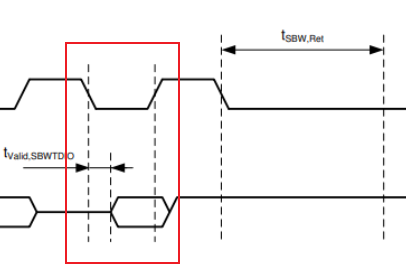

I'm reading through the documentation trying to understand the Spy-bi-wire operation. In the MSP430FR2100 datasheet (SLASE78D, Figure 5-15. JTAG Spy-Bi-Wire Timing), it shows that the SBWTDIO setup time starts before the falling edge of the SBWTCK signal, and the hold time ends after the rising edge of the SBWTCK signal (the text agrees with this as well). The diagram shows (and text alludes) that the SBWTDIO is held stable while SBWTCK is low.

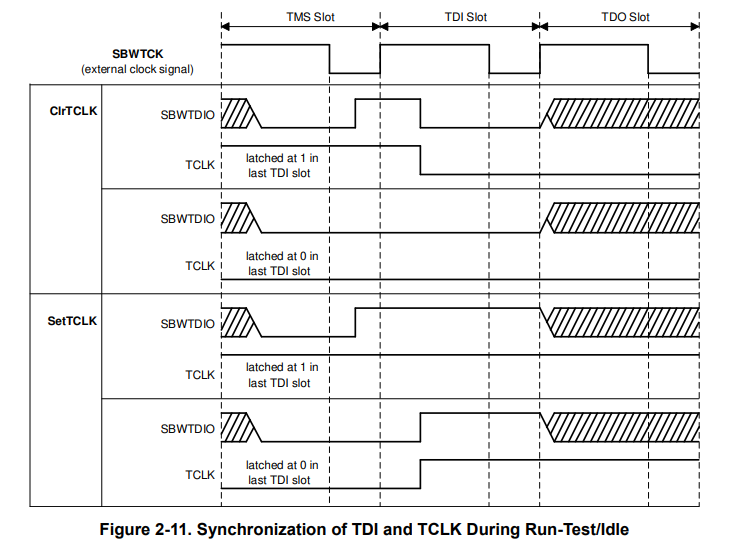

However, in the MSP430 programming guide (SLAU320AI, Figure 2-11. Synchronization of TDI and TCLK During Run-Test/Idle) it specifically shows the SBWTDIO changing while SBWTCK is low. The text also describes SBWTDIO needing to change specifically in the low phase of SBWTCK.

So these two pieces of text are contradicting each other. Or have I missed something?

What is the correct behavior/timing needed?