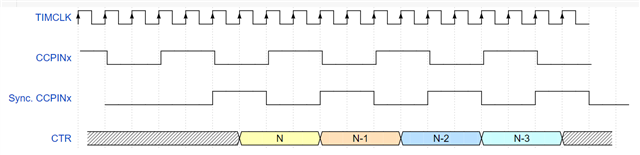

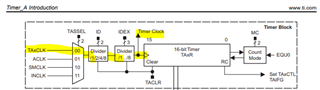

The data sheet seems to suggest that an external signal input to a timer module can be as high as the system frequency.

If the device operates at 25MHz, can the timer support up to 25MHz input signals, and still increment the counter every rising edge? This is assuming 50% duty cycle.

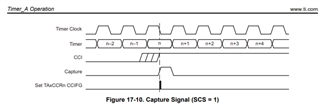

some devices like the CC26x0 suggest the need for one or two system clock periods to lock in the rising edge and update the count register...

Does this device update the count register on the rising edge of the first system clock after an edge was detected?

if so, how much time is needed from a signal falling edge, before the next rising edge can be detected and locked into the count register?