Other Parts Discussed in Thread: MSP430F2619

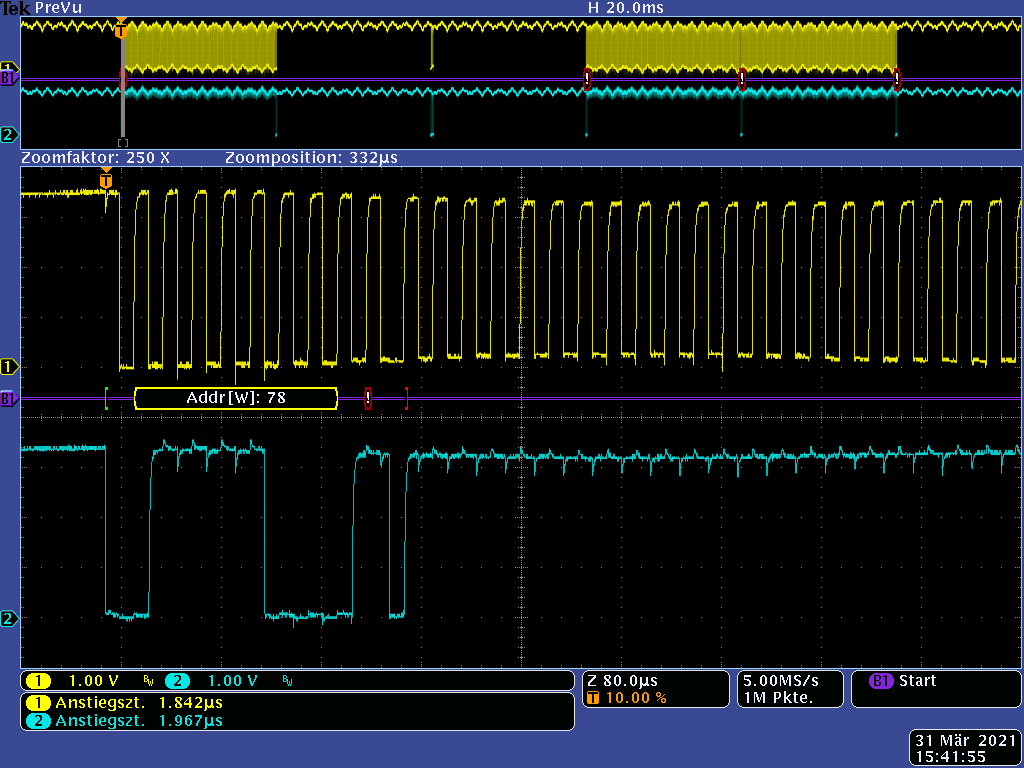

During an EMC test, we noticed the following:

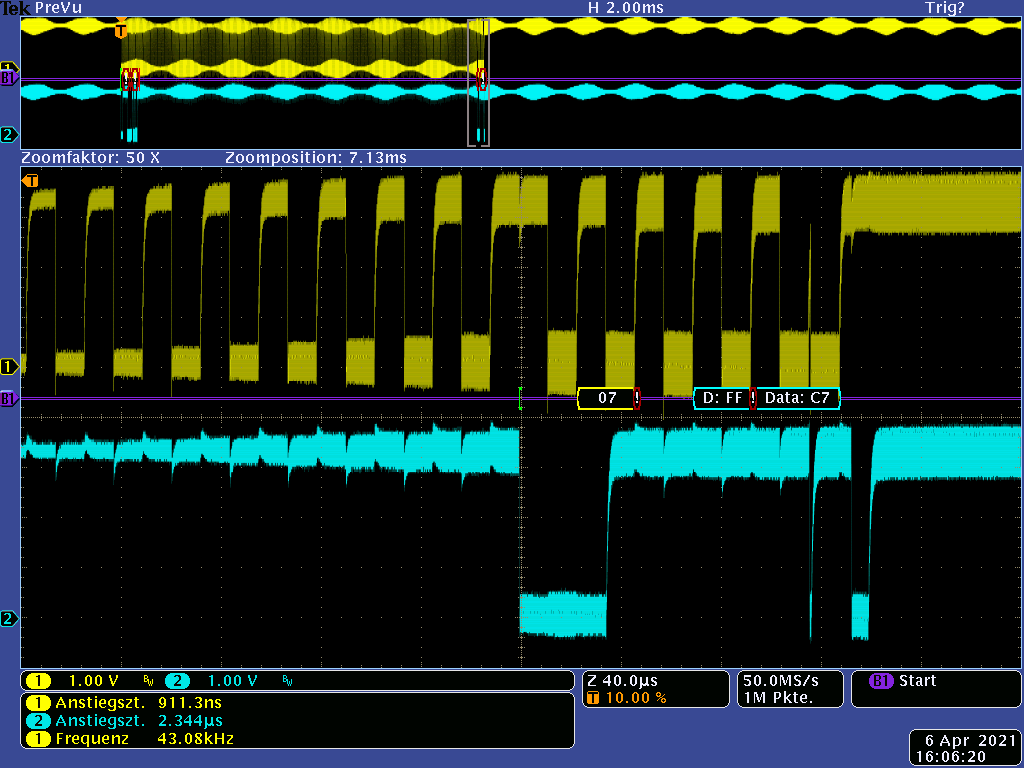

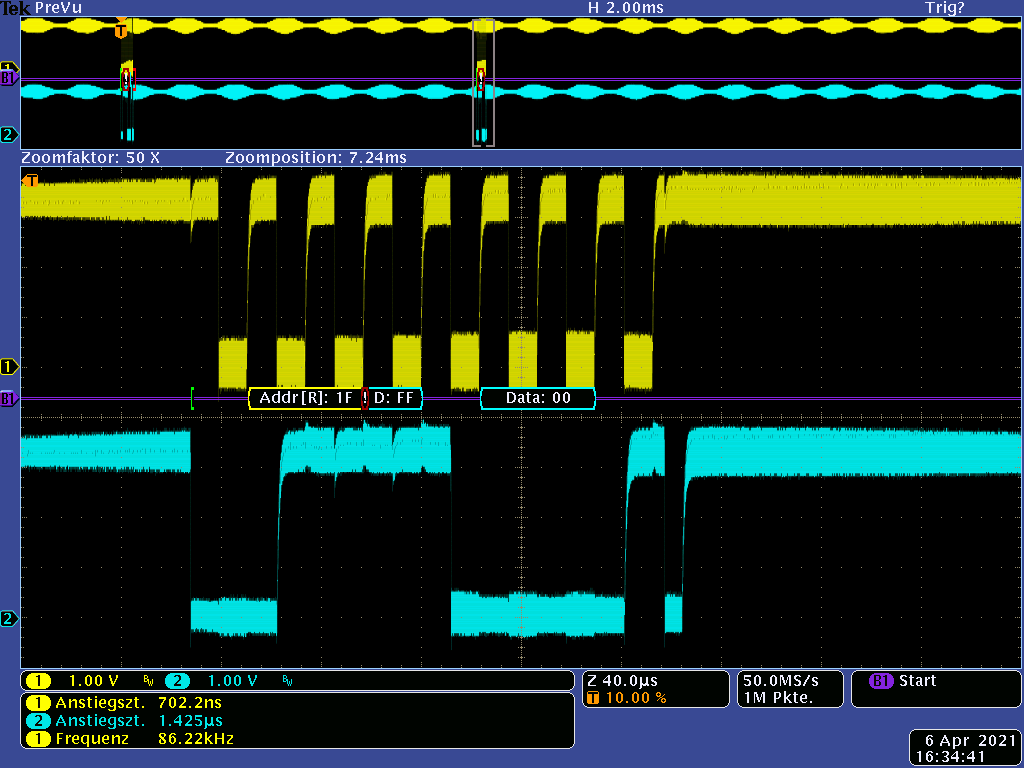

(ref to the enclosed image)

- Transmissions are aborted at the first 1-bit. We assume that the USCI detects an arbitration lost error at this point because the incoming RF distorts the signal.

- Why does the USCI continue to generate CLK clocks? Is there anything we can do to prevent this?

- Before the second transmission starts, the USCI is reset and reinitialized by software. The clock runs until this software-initiated reset. Why does it run until here?

- According to the Family Users Guide the UCALIFG will be set if the USCI detects an arbitration lost error. When UCALIFG is set the UCMST bit is cleared and the I2C controller becomes a slave. But after the UCMST is cleared the USCI should not generate any clock!!! (We operate all in single master mode and slave doesn't generate any clocks!)

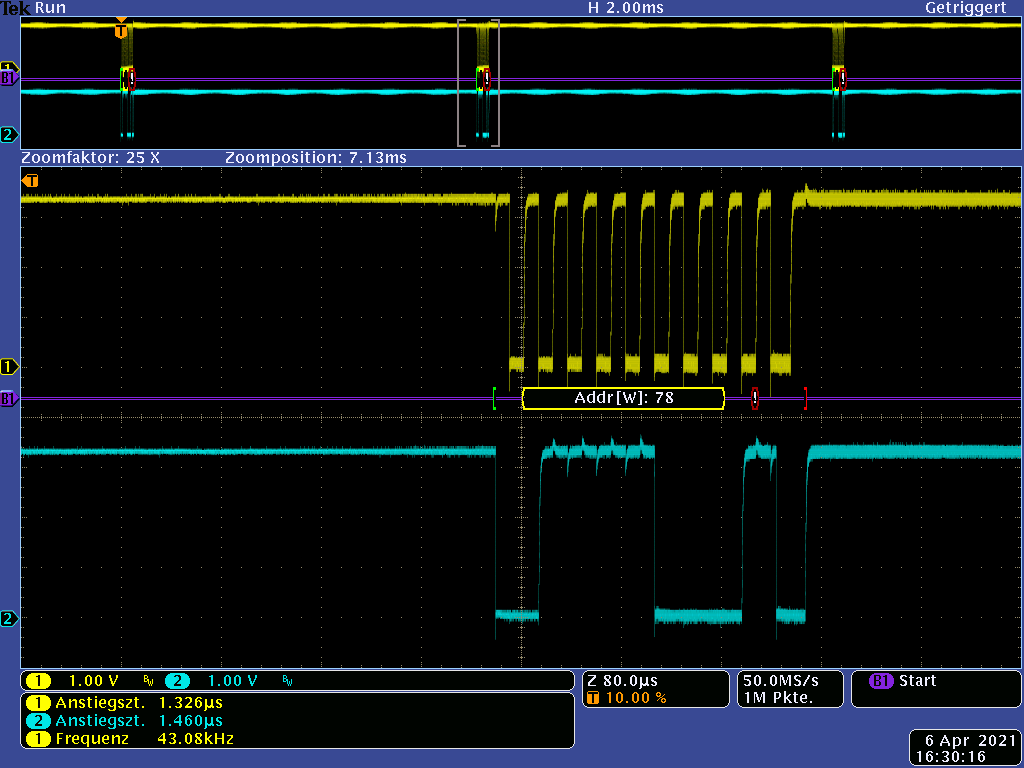

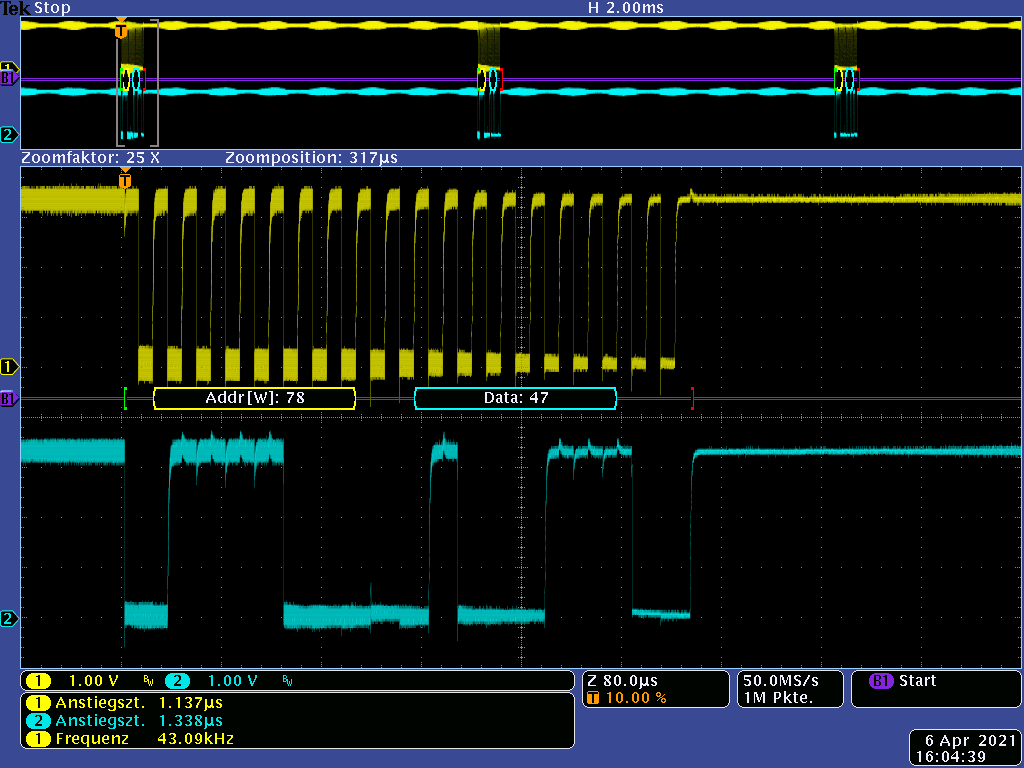

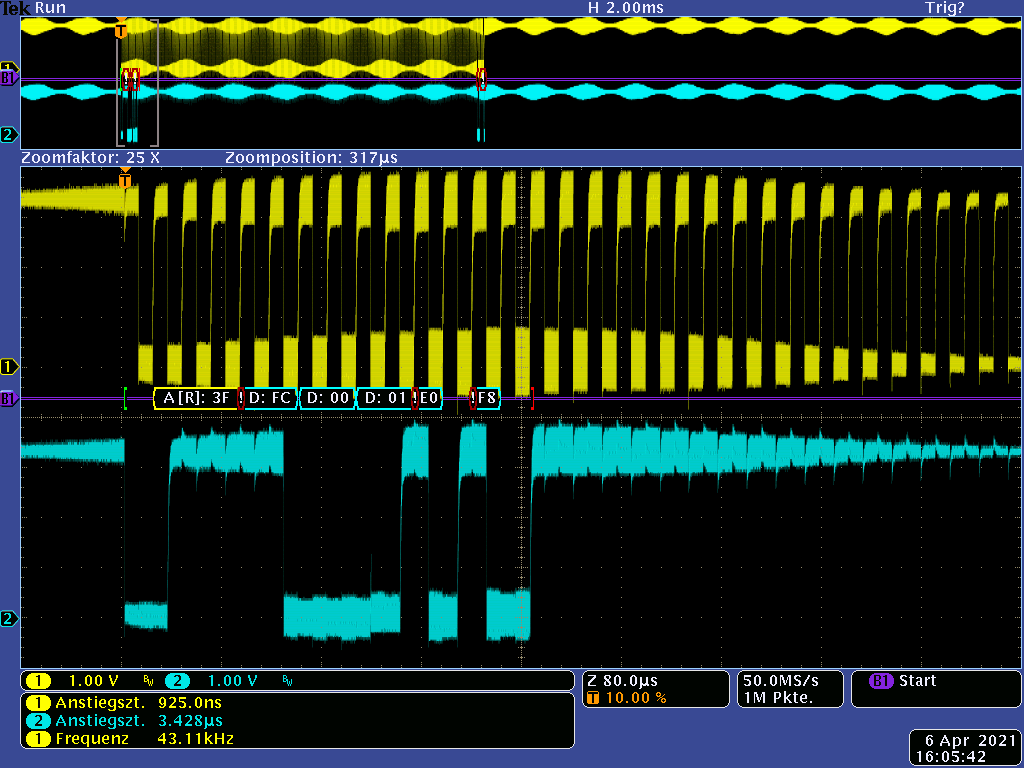

In addition, we also observed (next image) that the clocking continued even though the RF exposure had ended.

- SDA is permanently high. About 20 clocks can be seen. These must come from the USCI!

- Why does the USCI not stop? Because after 8 clocks and a NACK, the USCI should keep its feet still.

- How can the USCI get into this state?

We look forward to your response.

Thanks.

<<<<<<<<<<<<<<<<<<<<<<<<<< END OF THE FIRST POST >>>>>>>>>>>>>>>>>>>>>>>>>>>>>

Add on for the 3rd Post:

- Addressing the 0x78 with ACK looks correct.

- Addressing the 0x78 with ACK looks correct.