Hello,

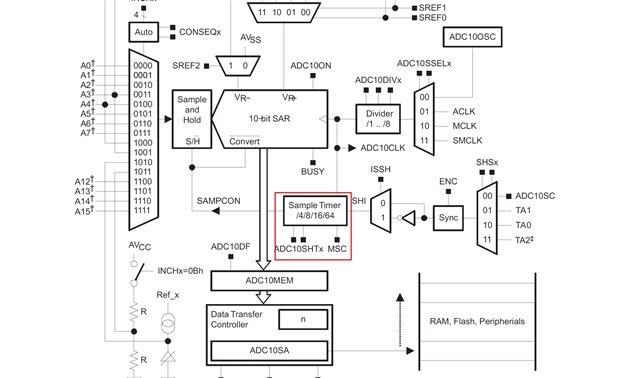

If I enable using ADC10DTC1 - it will hang the application I'm developing - here's a code snippet:

for (EVER)

{

ADC10CTL0 &= ~ENC; //

while (ADC10CTL1 & ADC10BUSY); // Wait if ADC10 core is active

ADC10DTC1 = 0x10;

ADC10SA = &adc_readings[0];

__no_operation(); // space for debugger

ADC10CTL0 |= ENC + ADC10SC; // Sampling and conversion start

__bis_SR_register(CPUOFF + GIE); // LPM0, ADC10_ISR will force exit

__no_operation(); // Set Breakpoint here

It hangs here.

The ISR just basically clears the CPUOFF bit.

If I disable using ADC10DTC1 and ADC10SA, I can read ADC10MEM just fine.

Thanks In Advance,

John W.