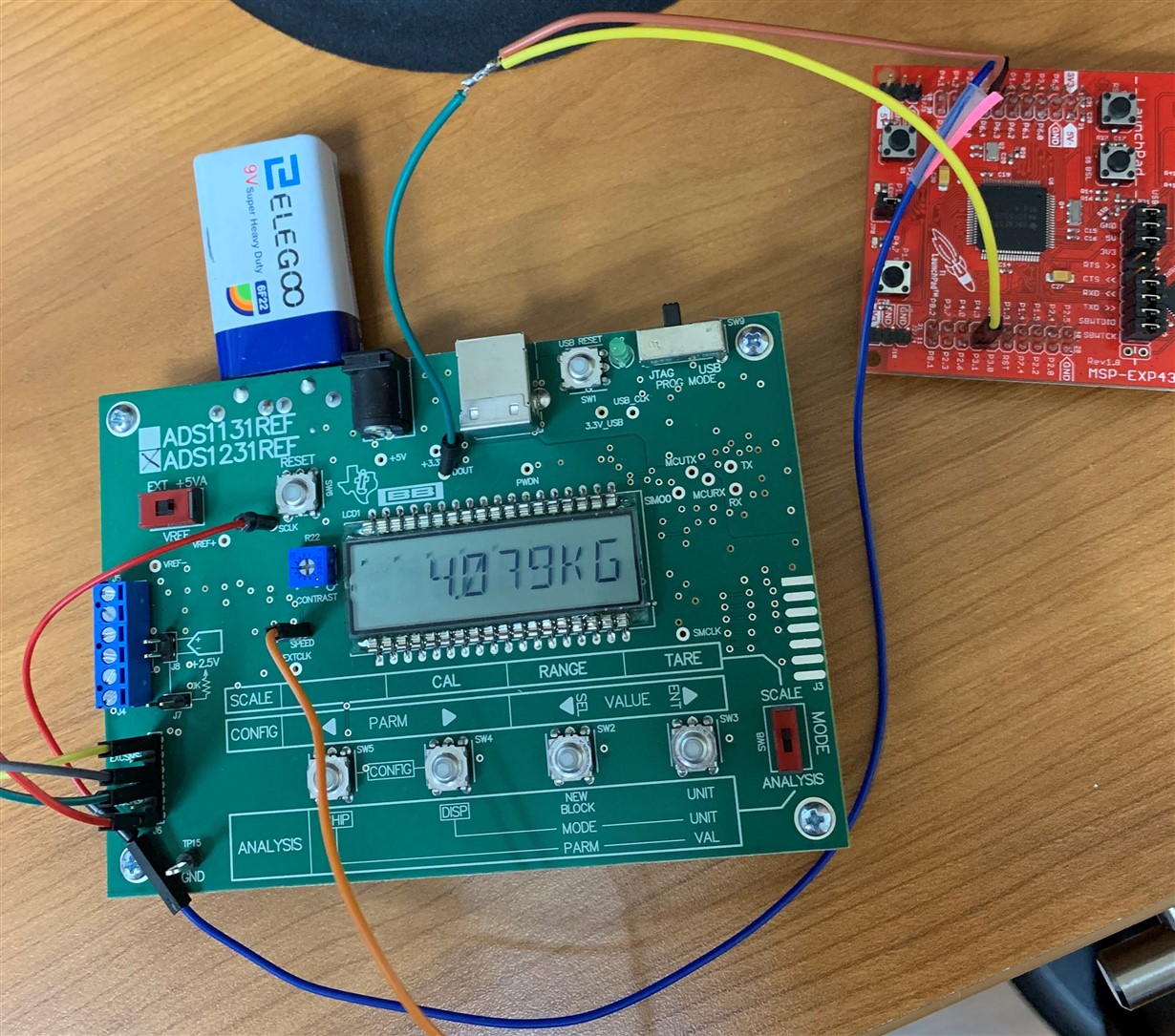

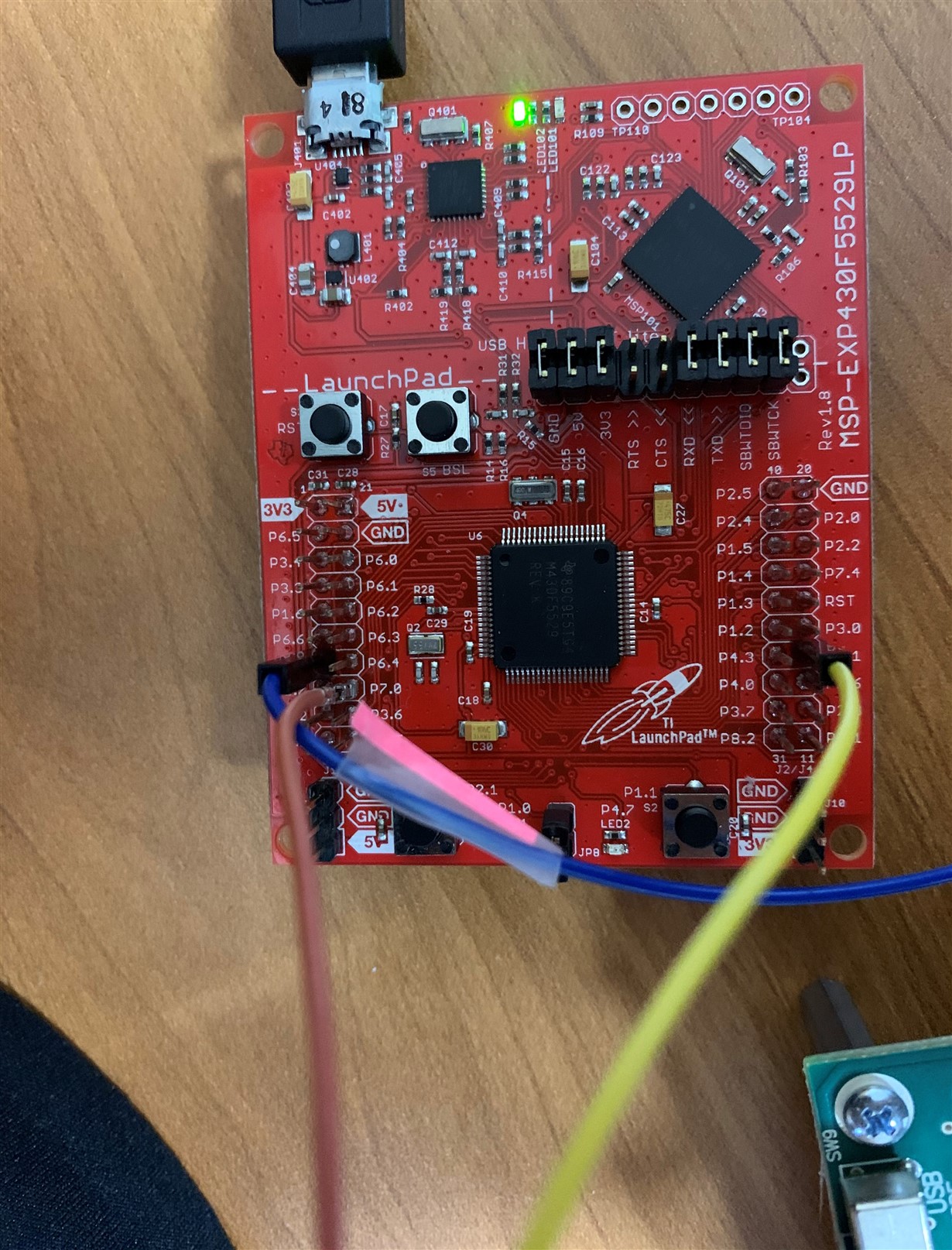

Other Parts Discussed in Thread: ADS1231, ADS1231REF, MSP430F449,

Tool/software: Code Composer Studio

Hi,

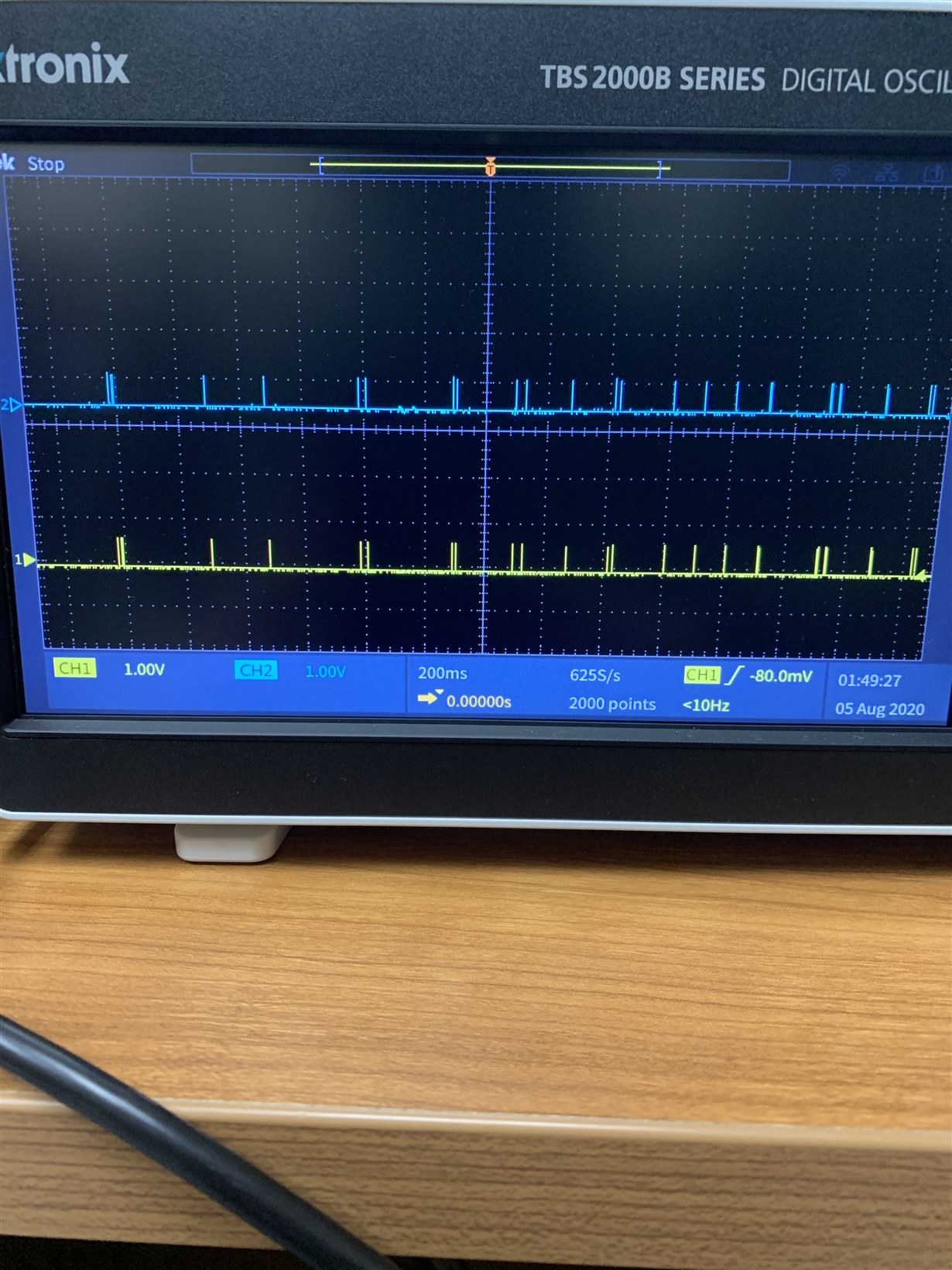

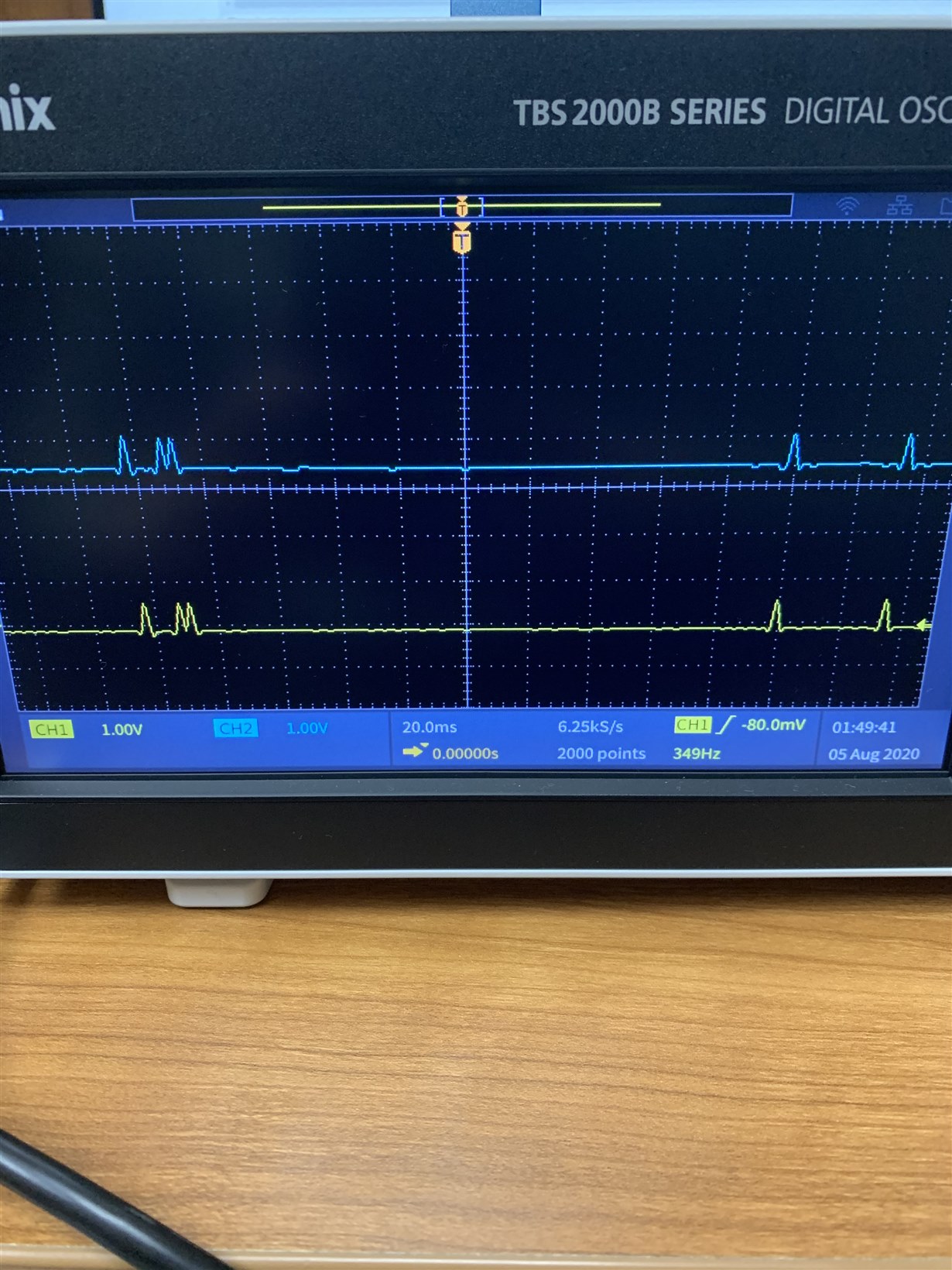

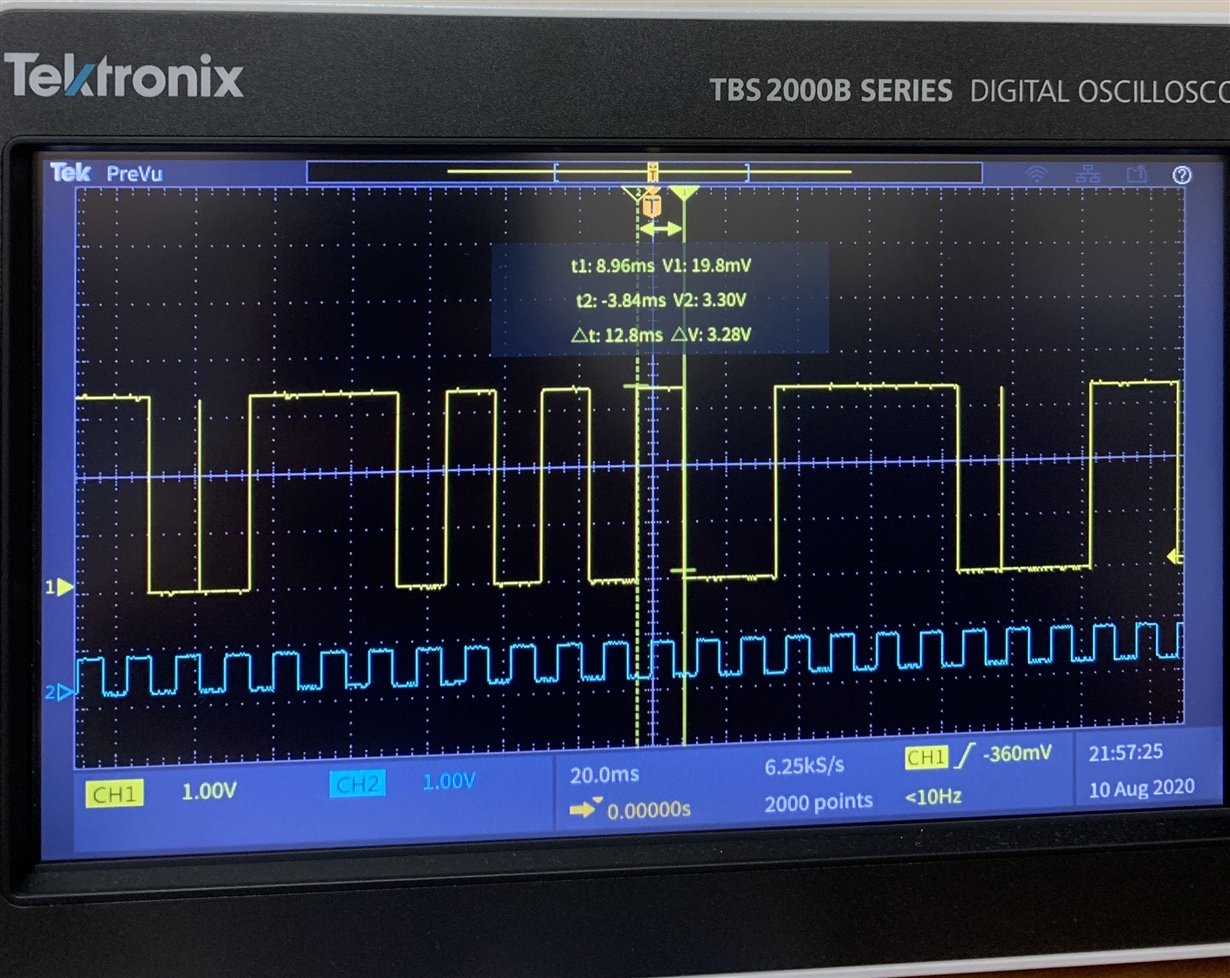

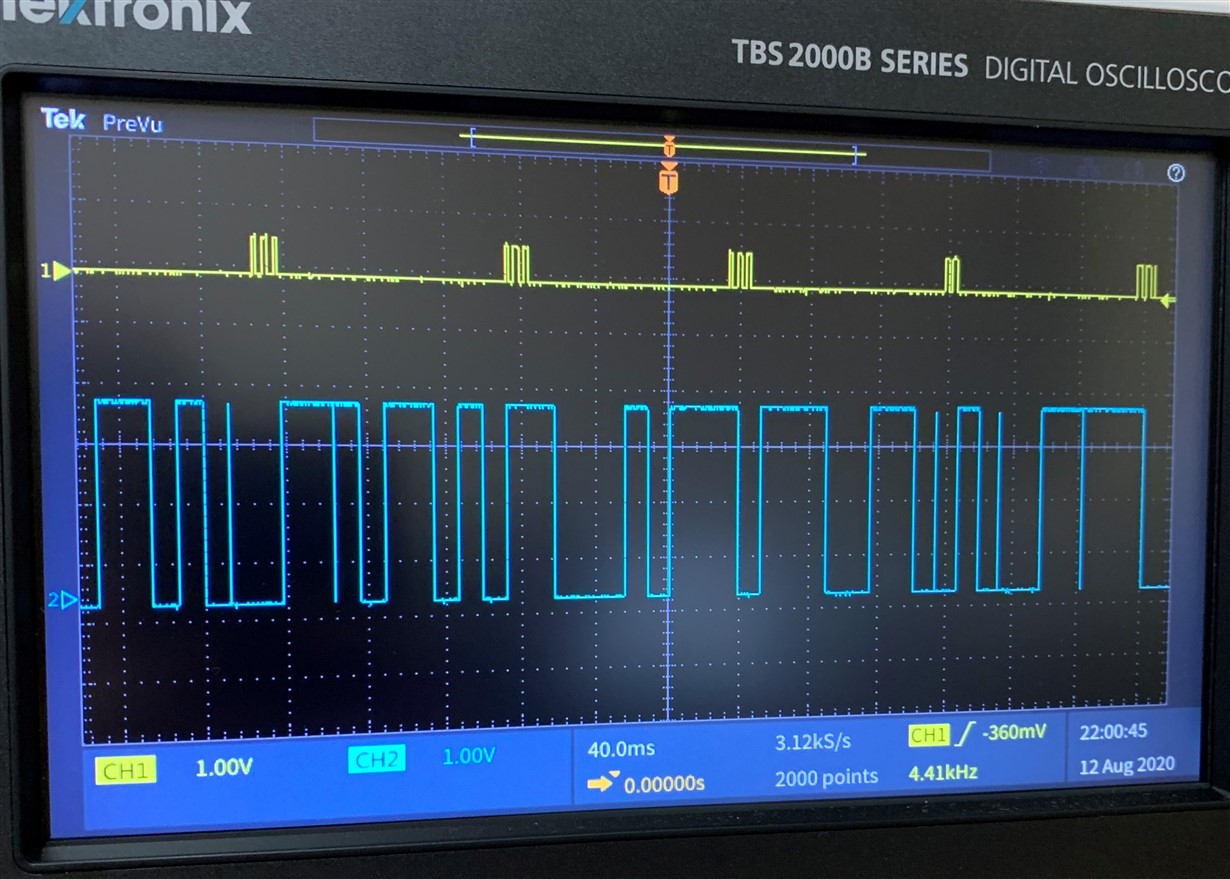

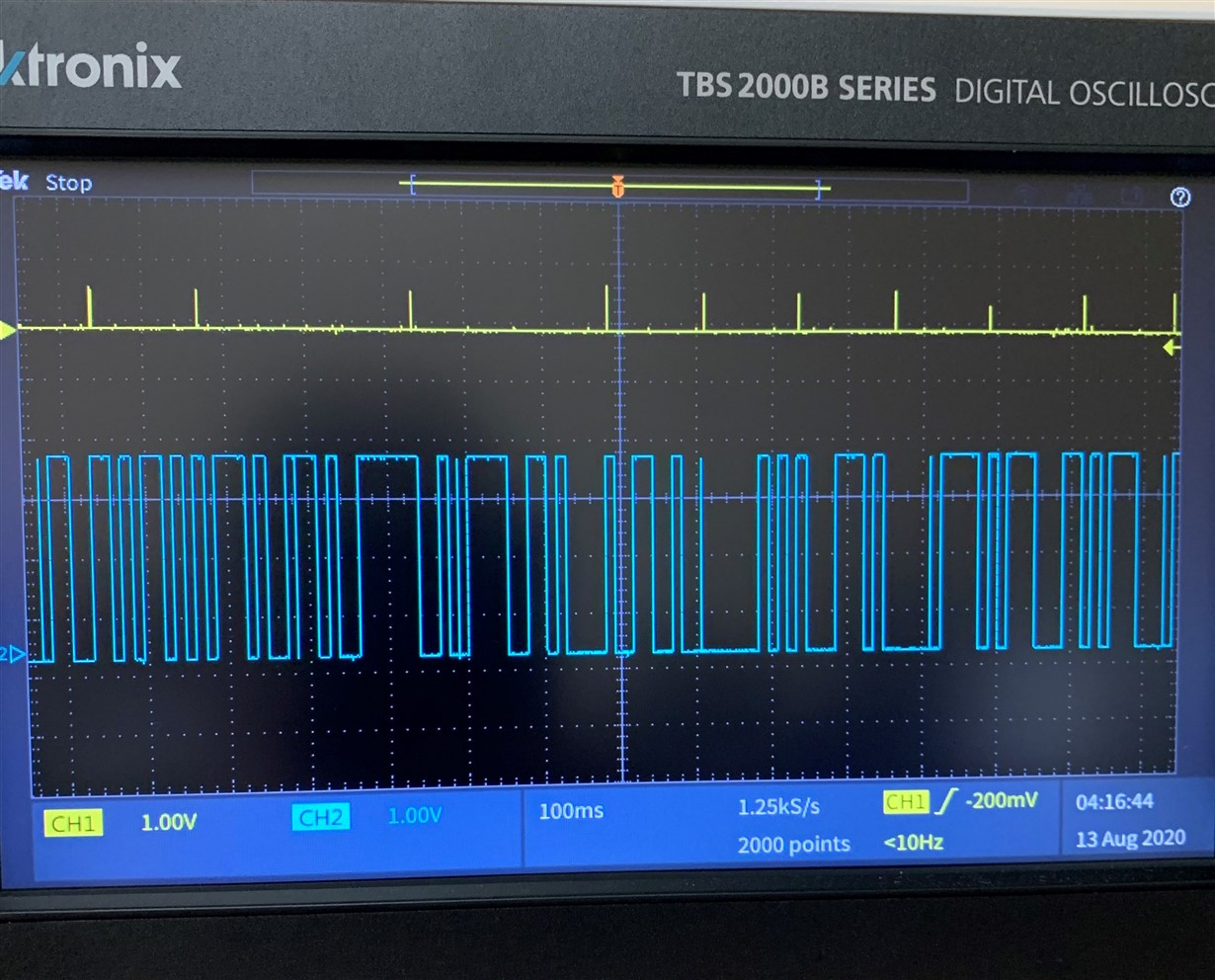

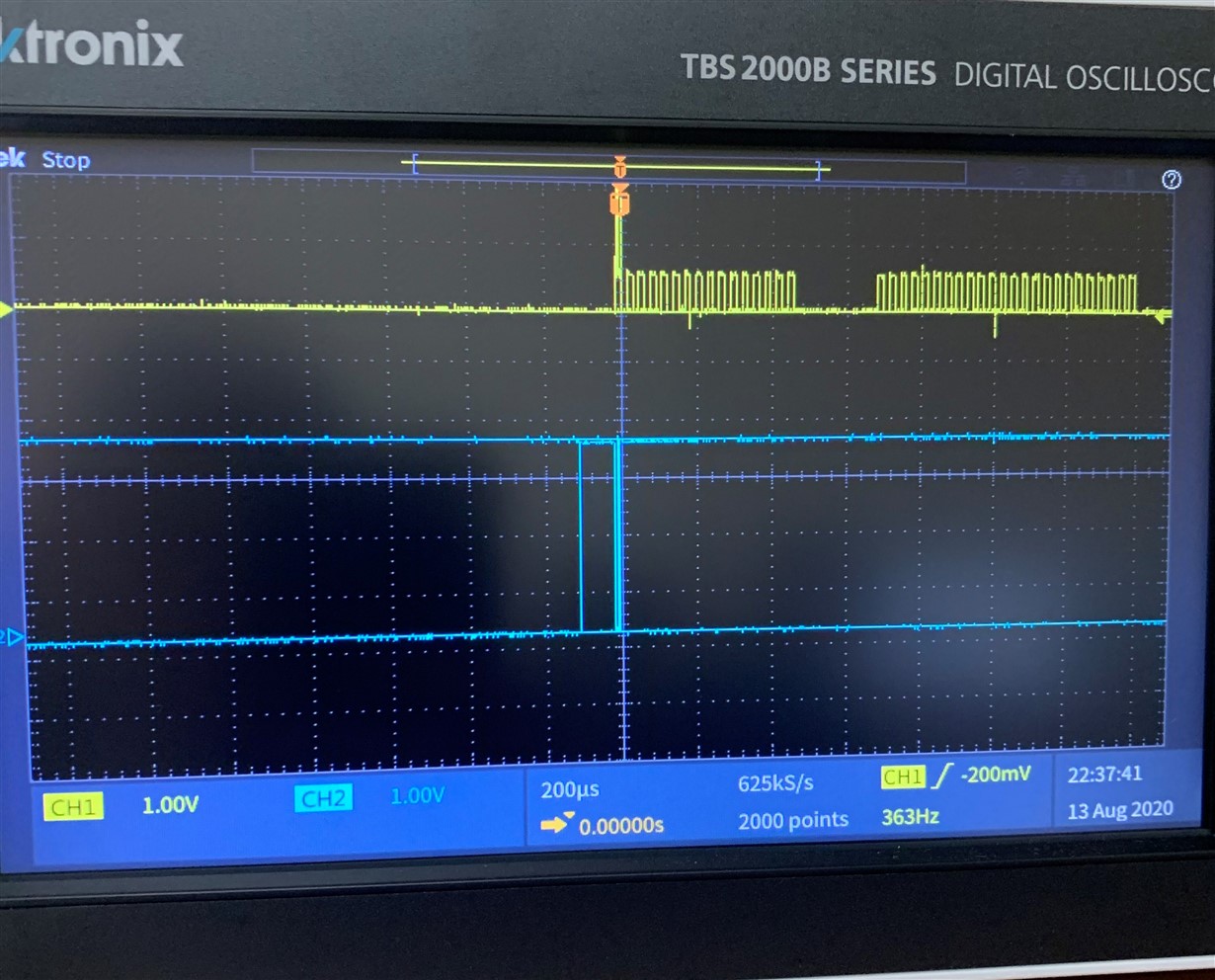

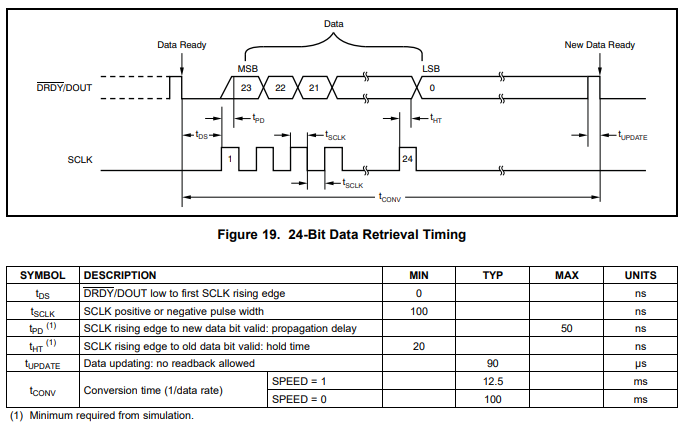

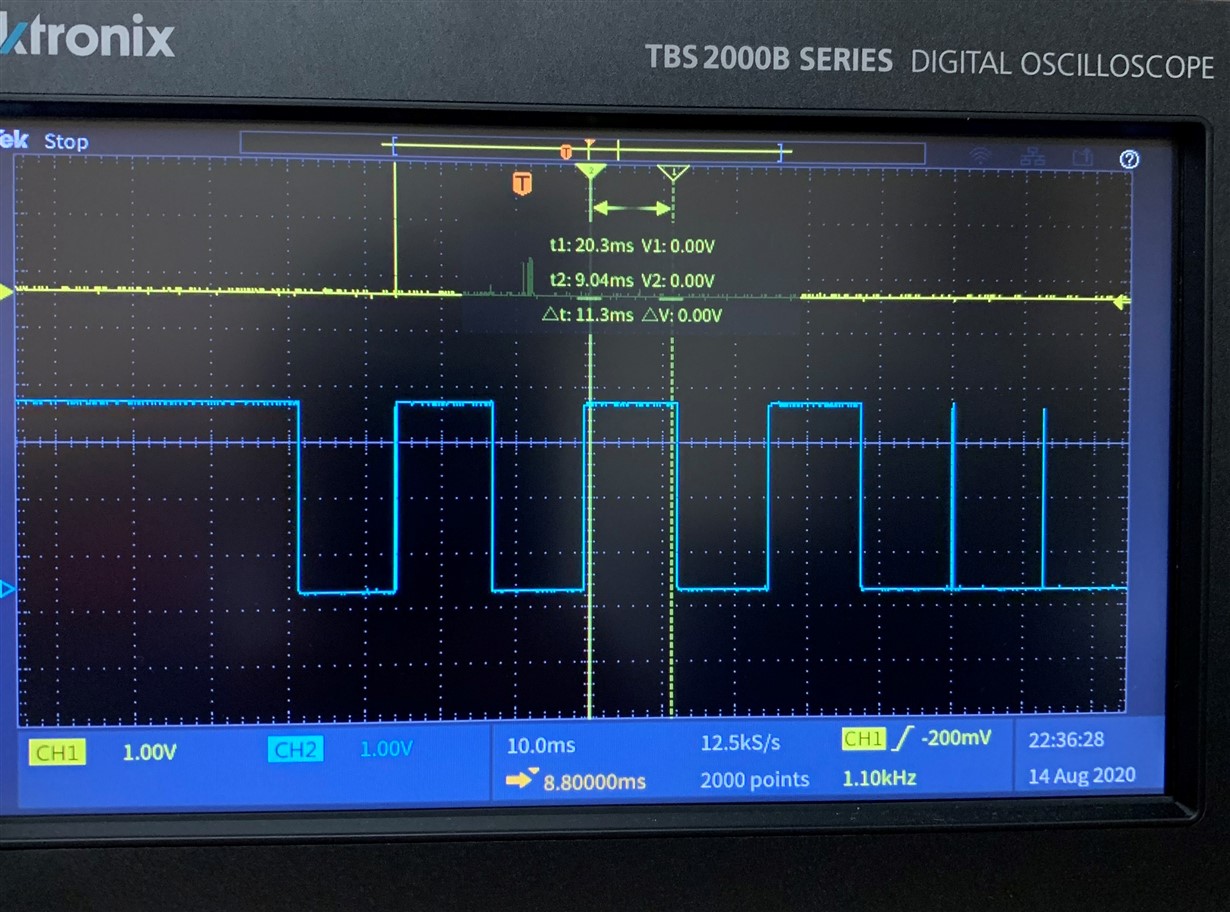

I'm trying to interface my ADS1231REF EVM with a MSP430F5529LP, but I'm not receiving any meaningful values in the receive buffer (UCB0RXBUF). I configured the SPI registers and made the proper pin connections. DOUT of the ADS1231 is connected to the MISO pin (P3.1) and P7.0 of the MSP430 and SCLK of the ADS1231 is connected to the MSP430's UCB0 clock output (P3.2). According to its datasheet, the ADS1231 is ready to transmit data when its DOUT signal goes low, so I monitor P7.0 in my code. When I connect my osciloscope to the MISO pin of the MSP430, I see the correct data being outputted from the ADS1231REF board, but the only values I receive in the receive buffer in Code Composer is similar to the following console log:

The adc_data is 3fffff.

The adc_data is 0000.

The adc_data is ffffffff.

The adc_data is 0000.

The adc_data is 0000.

The adc_data is 0000.

The adc_data is 0000.

The adc_data is ffffffff.

The adc_data is fffff.

The adc_data is ffffffff.

The adc_data is 0000.

The adc_data is ffffffff.

The adc_data is ffffffff.

Attached is my code. I would really appreciate any help to solve this problem.

Thank you

#include <msp430.h>

#include <stdio.h>

int32_t data1, data2, data3, signExtension, adc_data;

char sign;

void SPI_init()

{

UCB0CTL1 |= UCSWRST; // software reset enable

UCB0CTL0 = UCMST + UCSYNC + UCMODE_0 + UCMSB + UCCKPL;

UCB0CTL1 |= UCSSEL_3; // select SMCLK

UCB0BRW = 109; // 1 MHz / 109 = 9600 bps

P3SEL = BIT0 + BIT1 + BIT2; // configure SPI pins

P7DIR &= ~BIT0; // P7.0 = DRDY, set as input

P7OUT |= BIT0;

UCB0CTL1 &= ~UCSWRST; //software reset disable

}

int main(void)

{

SPI_init(); // configure SPI registers

while (1) // infinite loop

{

while (!(P7IN & 0x01)); // is DRDY/DOUT low / is ADS1231 ready to Tx data?

while (!(UCB0IFG & UCTXIFG));

UCB0TXBUF = 0x00; // transmit dummy value

while (!(UCB0IFG & UCRXIFG));

data1 = UCB0RXBUF;

sign = data1 >> 7;

if (sign) signExtension = 0xff;

else signExtension = 0x00;

signExtension <<= 24;

data1 = data1 << 16;

while (!(UCB0IFG & UCTXIFG));

UCB0TXBUF = 0x00;

while (!(UCB0IFG & UCRXIFG));

data2 = UCB0RXBUF;

data2 = data2 << 8;

while (!(UCB0IFG & UCTXIFG));

UCB0TXBUF = 0x00;

while (!(UCB0IFG & UCRXIFG));

data3 = UCB0RXBUF;

adc_data = data1 + data2 + data3 + signExtension;

printf("The adc_data is %04lx.\n", adc_data);

}

}