Hello friends,

Configure GPTM3 full wide for Oneshot interrupt timeout event and reload 1 second value inside interrupt handler cycles.

GPTM3 CLK source: 16MHz PIOSC (65.5ns)

Load value: 0xF42400 (16,000,000 * 65.5ns = 1 second one shot interval)

The problem is one shot period measured via scope probe GPIO port (1sec) intervals are stable until PWM0 is active. The one shot load time interrupt starts to widen >1.1 seconds (>100ms), seemingly depending on how often PWM0 is being interrupted for duty cycle updates. Why would the load value not hold the interrupt period fairly consistent to/with the down count time out expiration? It seems to be some kind of odd errata in the down count timer load value expiration and triggering the vectored interrupt handler. The Oneshot is enabled inside an edge count timers CCP interrupt event. We don't really care how often the edge count interrupt occurs in this scenario. Yet don't believe the Oneshot should ever allow or process count reloads until the previous count expires.

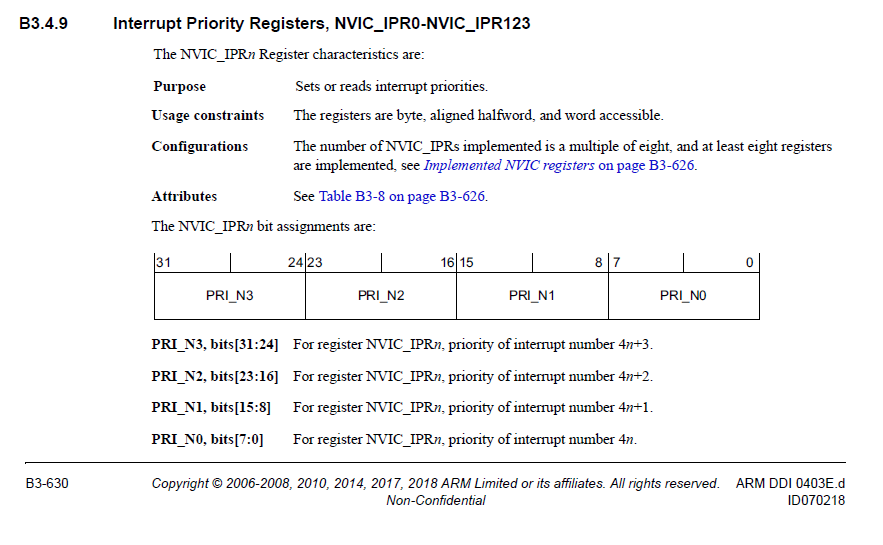

Is it not unreasonable to expect reload period drifts <16.6ns (<2 x SYSCLK (8.3ns)) NVIC running 120MHz? Is there a work around to have exact 1 second time interval not be impacted by other interrupt sources? The drifting interrupt handler (>100ms) stray even wider when GPTM clock 120MHz. Is it better to re-load the one shot load value outside the handler of the INT vector call-ed/er? Something odd is occurring to have Oneshot interval stray >100ms in the reload value grow uncontained in the process.